반응형

여러분들 반도체 소자 카테고리에서 High-k 소재에 대해서 배우셨습니다. 정전용량을 높이기 위해서 High-k 소재가 도입되었는데, 오늘은 그 High-k 소재의 특성에 대해서 다루어보도록 하겠습니다. 그리고 반도체 공정에서 Low-k 소재도 매우 중요합니다. 함께 다루어보겠습니다.

[질문 1]. High-k 소재가 도입된 이유에 대해서 설명하세요.

High-k 소재의 도입은 집적도를 높이는 데에서 시작합니다. 소자 Dimension이 미세화되면서 Subthreshold leakage current를 억제하기 위해 gate oxide thickness가 점점 얇아졌습니다. oxide thickness를 줄이는데 한계에 봉착하게 되면서 High-k 소재가 도입되었습니다. Transistor의 크기가 작아지면서 oxide의 면적 또한 줄어듭니다. 따라서 면적을 넓히는 것은 쉽지 않기 때문에, oxide thickness를 줄이는 노력이 시작되었습니다. 기존 gate oxide 소재였던 SiO2는 10nm 이하까지 thickness를 줄였지만, 박막이 너무 얇아진 탓에 tunneling과 같은 현상으로 누설전류가 증가하게 되었습니다. 그래서 적정 oxide 두께를 가지면서 효과적으로 채널에 전하를 모을 수 있는 High-k 소재가 도입된 것입니다.

[꼬리 1.1]. High-k의 의미가 무엇인지 설명하세요.

'High-k'는 고유전율을 의미합니다. 여기서 유전율은 전기장이 인가될 때, 전하를 잡아두는 정도를 나타내는 척도입니다. 따라서 High-k 소재는 고유전율 소재로 같은 전압을 인가하더라도 다른 소재보다 더 전하를 잡아둘 수 있습니다. 이러한 유전율의 원리는 절연막의 특징은 '분극 현상' 때문입니다. 게이트에 전압을 인가하게 되면 절연막을 구성하는 원자는 원자핵과 전자로 분리가 되는 분극현상이 나타납니다. 이때, 유전율이 클수록 분극이 잘 일어나고 원자핵(+)과 전자(-)의 늘어나는 정도가 커지게 됩니다. MOSFET에 High-k 소재를 gate oxide로 도입할 경우, gate에 양전압을 인가하게 되면 절연막의 위쪽은 (-), 하단은 (+)로 분극이 형성됩니다. 그렇기 때문에, gate oxide 하부막에 전자를 더 효율적으로 모을 수 있게 됩니다.

[꼬리 1.2]. 그럼 무조건 높은 유전율의 소재를 사용하면 소자 성능이 향상되겠습니다?.

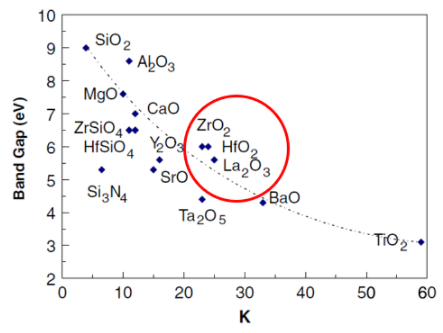

그렇지 않습니다. High-k 소재일수록 분극이 잘 일어나게 되면서 효율적으로 채널층의 전하를 모을 수 있습니다. 하지만 High-k 소재는 분극이 잘 일어나는 만큼 원자 내 결합이 약하기 때문에 유전율이 너무 높은 소재를 사용할 경우 누설전류가 오히려 증가할 수 있습니다. 실제로 유전율이 증가할수록, 소재의 energy bandgap은 작아지는 반비례 관계에 있습니다. SiO2는 3.9의 유전율을 가지지만 ~9.1eV의 높은 밴드갭 특성으로 5MeV의 breakdown voltage를 가지는 등 절연특성이 매우 우수했습니다. 하지만 TiO2와 같이 83~100의 유전율을 가지는 High-k 소재는 3.05eV의 낮은 Energy bandgap을 가지므로 TiO2를 gate oxide로 사용할 경우 누설전류가 크게 증가할 것으로 보입니다. 그래서 이러한 trade off 관계를 고려하여 현재는 20~25의 높은 유전율과 5.8eV의 적절한 Energy bandgap을 갖는 HfO2가 High-k 소재로 채택되었습니다.

[꼬리 1.3]. SiO2에서 HfO2 소재를 사용하면 유리한 점을 공정적인 관점에서 설명하세요.

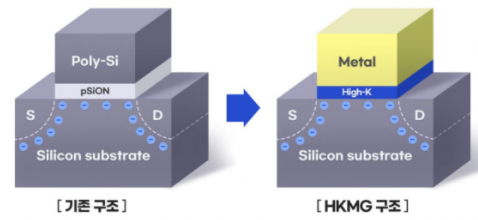

SiO2의 유전율은 3.9 HfO2는 20~25로 SiO2 대비 5배가 높습니다. 이는 같은 게이트 전압을 인가하더라도 같은 면적과 두께라면 절연막 아래 반전층의 전하 밀도는 SiO2 보다 HfO2가 5배는 높다는 것을 의미합니다. 이는 다시 말하면 채널에 동일한 전하밀도를 형성하기 위해서 HfO2는 SiO2보다 5배 두꺼운 oxide thickness를 가져도 된다는 것을 의미합니다. 기존 SiO2의 박막이 얇아지면서 발생했던 누설전류를 억제할 수 있음을 의미합니다. 그리고 SiO2에서 HfO2 소재로 바뀌면서 기존 게이트 소재인 Poly-Si에서 Metal 기반 소재로 바뀌게 됩니다. 이렇게 gate 소재가 바뀌게 되면서 High-K Metal Gate, HKMG 공정이 도입되었습니다. Capacitor에 전하를 축전하여 정보를 저장하는 DRAM에서 또한 Capacitor의 유전체로 High-k 소재인 ZrO2, 지르코늄옥사이드가 사용되고 있습니다.

[꼬리 1.4]. High-k에서 Metal gate가 도입된 이유에 대해서 설명하세요.

하단 링크 참조.

[반도체 소자] : "HKMG에 대해서 설명하세요"

HKMG는 High-k Metal Gate의 약어로 앞선 교육에서 게이트의 영향력을 향상시키기 위해서 도입된 기술입니다. 최근 삼성에서 512GB DDR5 차세대 DRAM에서 HKMG 공정을 첫 도입해서 전력소모를 약 13% 감소시

sshmyb.tistory.com

[꼬리 1.5]. High-k 소재의 단점은 없나요?

High-k 소재는 기존 SiO2 대비 고유전율이라는 소재 본연의 장점이 있지만 SiO2 자체의 장점을 Cover하지 못합니다. SiO2는 화학적, 열적으로 안정적이고 Si 기판위에서 Conformal하게 균일한 박막을 형성할 수 있다는 점, 기존 게이트 소재인 Poly-Si와 접착도가 높다는 점. 이러한 SiO2의 장점들이 High-k에서는 공정적 이슈로 작용합니다. 그래서 공정적으로 High-k 소재는 현재 Atomic Layer Deposition, ALD 원자증착법으로 10nm 이하 두께의 박막을 형성합니다. ALD로 우수한 막질의 박막을 형성한다고 하더라도, Si 기판과의 계면 특성이 좋지 않다는 단점이 존재합니다. 그렇기 때문에 계면에서 전하 캐리어의 이동이 원활하지 않아 전류특성에 영향을 끼칩니다. 그리고 현재 High-k 소재 또한 점점 두께가 얇아지면서 SiO2보다 낮은 Energy bandgap으로 절연특성이 뛰어나지 않아 누설전류의 이슈가 발생하고 있습니다. 그래서 현재는 HfO2를 대체할 수 있는 새로운 High-k 소재에 대한 연구가 활발히 진행되고 있습니다.

[질문 2]. Low-k 소재가 도입된 이유에 대해서 설명하세요.

Low-k 소재는 유전율이 낮은 소재입니다. 즉, 전기장 내에서 전하를 잡아두는 힘이 약한 소재입니다. Low-k소재는 배선과 배선 사이의 short 되는 것을 방지하기 위해 사용됩니다. 이때 Low-k 절연막이 상당히 유용하고 요구되는 상황입니다. 만일 배선과 배선 사이를 High-k 소재로 채울 경우, Metal-Oxide-Metal, MOM Capacitor 구조가 형성되면서 배선에서 전하를 잡아두는 성질 때문에 전하의 흐름이 원활하지 않아 RC Delay 신호지연현상잉 발생합니다. 이러한 이슈를 극복하기 위해서 Low-k 절연막이 사용되는 것입니다. 최근 반도체 칩들은 집적도가 높고 회로가 점점 더 복잡해지고 있습니다. 복잡한 회로 내에서 신호지연현상은 소자 성능에 큰 악영향을 미칠 수 있기 때문에 Low-k 소재 역시 반도체 성능 향상에 큰 영향을 미친다고 할 수 있습니다.

반응형

그리드형(광고전용)

'반도체사관학교 훈련과정 > 반도체 물리 및 소재' 카테고리의 다른 글

| [반도체 소재] "Plug W(텅스텐) grown on CVD" (10) | 2022.02.11 |

|---|---|

| [반도체 소재] "Si3N4, SiON grown on LPCVD & PECVD" (0) | 2022.02.10 |

| [반도체 소재] "SiO2 grown on LPCVD & PECVD" (10) | 2022.02.10 |

최근댓글