반응형

오늘은 Process Control Monitor, PCM에 대해서 공부를 해보았습니다.

PCM은 반도체 Process 과정에서 측정한 Parameter들을 기반으로 원하는 Spec에 맞게 제작되었는지 파악하는 과정입니다.

설계적인 측면에서 왜 이러한 불량 분석이 발생했는지, 불량이 Timing에 관한 Margin 성 불량 이슈인지, Simulation과 측정 데이터가 matching 되는지 공정이슈는 없는지.

오늘부터 PCM이 익숙해질 때까지 달려보겠습니다.

이번 장에서는 PCM의 주요 Parameter에 대해서 알아보도록 하겠습니다.

[질문 1]. Process Control Monitor, PCM에 대해서 설명하세요.

반도체 공정을 진행한 Wafer에 형성되는 Transistor, 저항, Diode, Capacitor 등 각종 Active, Passive 소자의 전기적 특성을 측정함으로써 공정 진행 상태를 파악할 수 있는 Parameter를 추출하는 과정을 PCM Parameter 측정이라고 합니다. 이를 위해서 Wafer에서 구현되는 회로를 대변하는 각종 소자들의 적절한 전기적 특성을 획득하기 위해 Test Pattern을 제작합니다. 각각의 소자는 Test Pattern을 통해 Parameter를 추출할 수 있습니다.

[질문 2]. Transistor 측정 대해서 설명하세요.

Transistor는 Gate, Drain, Source, Body, 4단자 소자입니다. 보통 Source는 특별한 경우를 제외하고 Ground에 연결되어 있습니다. PCM 측정에서 Source를 제외한 3개의 단자를 Variable 1, Variable 2, Constant로 놓고 측정을 진행합니다. Variable 1은 말 그대로 변하는 값, 변수이므로 측정과정에서 Sweep 하여, 특성 값을 얻어냅니다. (X축) Variable 2는 특정 다수의 값을 가지며, Constant는 일정한 1개의 값을 가집니다. MOSFET의 Output Characteristics, (Id-Vds)를 보면 Drain Voltage, Vds는 Variable 1, Drain Current, Id는 Variable 2, Vbs는 Constant에 해당합니다.

[꼬리 2.1]. Transistor에서 대표적인 PCM Parameter에 대해서 설명하세요.

Transistor의 대표적인 PCM Parameter는 ①Threshold Voltage (Vt), ②Saturation Threshold Voltage (Vtsat), ②Saturation Drain Current (Idsat), ③Leakage Current (Ioff), ④DIBL parameter, ⑤Subthreshold slope(S-factor), ⑥Maximum Substrate Current (Isubmax), ⑦Drain-to-Source Breakdown Voltage (BVdss), ⑧Body Factor (γ)이 있습니다.

[꼬리 2.2]. Threshold Voltage, Vtext에 대해서 설명하세요.

Threshold Voltage는 MOSFET의 Channel이 형성되는 Gate 전압으로 Silicon Surface에 Minority Carrier Density가 Bulk의 Carrier Density와 같아지는 Strong Inversion 상태가 일어나는 Gate Voltage를 의미합니다. Vt 측정방법은 Source와 Body를 Ground 상태에 놓고, Drain, Vds=0.05V를 인가한 후, Gate Voltage, Vgs를 Sweep 함으로써 Ids-Vgs 특성을 측정한 후 Maximum gm (Transconductance, = ΔIds/ΔVgs) Point에 접선을 그어 Vgs 축 절편을 구한 후 1/2Vds를 뺀 값이 바로 Vt 전압입니다.

Channel Length가 감소하면서 Short Channel Effect, SCE가 발생하며 Vt가 작아지는 Vt roll-off 현상이 심해집니다. 그리고 Channel Width가 감소하면서 LOCOS 구조의 Isolation의 경우 Vt가 증가하는 Vt roll-up 현상이 발생하는 Channel Width Effect, 또는 STI Isolation의 경우 Edge의 Electric Field에 의해 축적된 Positive Charge Ion이 Vt를 낮추어 Vt roll-off 현상이 발생하는 Reverse Channel Width Effect가 있습니다.

[꼬리 2.3]. Saturation Threshold Voltage, Vtsat에 대해서 설명하세요.

MOSFET 동작시 Drain에 동작전압을 인가할 경우 Threshold Voltage로 Ids=10nA*W/20가 흐르는 전압을 Vtsat으로 정합니다. 이떄, Wide width의 기준은 20um입니다. Vtsat의 측정방법은 역시 Source와 Body를 Ground 상태에 놓고, Drain에 전압을 인가한 상태에서 Gate Voltage, Vgs를 Sweep 함으로써 Ids=10nA/20um인 Vgs가 Vtsat으로 정의합니다. Channel Length가 감소함에 따라 Vtsat이 감소하고, 소자의 Margin 평가에서 많이 사용됩니다. 일반적으로 Short Channel에서 Idsat이 증가하면, Vtsat 또한 증가합니다.

[꼬리 2.4]. Saturation Drain Current, Idsat에 대해서 설명하세요.

Drain과 Gate에 동작전압을 인가했을 때의 Drain Current로 Threshold Voltage와 함께 소자 특성을 결정하는 핵심 Parameter입니다. Idsat은 소자의 Performance와 회로의 Speed 등 성능을 결정하는데 활용됩니다. Idsat을 측정하는 방법은 Source와 Body는 Ground 상태에 놓고, Drain에 동작전압을 인가한 후에 Gate Voltage를 0V에서 동작전압까지 Sweep 시켜 Ids-Vgs 특성을 측정합니다. Vgs=동작전압일 때의 Drain Current가 바로 Idsat입니다.

[꼬리 2.5]. Leakage Current, Ioff 측정 방법에 대해서 설명하세요.

Channel이 형성되기 전 Subthreshold Region에서 흐르는 Current로 Drain과 Bulk, Source 간의 Diffusion Current 입니다.Ioff를 측정하는 방법은 Source와 Body를 Ground 상태에 놓고, Gate에 전압을 0V에서 동작전압까지 Sweep 함으로써 Ids-Vgs 특성을 측정합니다. 이때 Ids=10nA/20um에서 Ids에 접선을 그어 Ids축 절편이 바로 Ioff 입니다. 일반적으로 Channel Length가 짧아지면서 Short Channel Effect에 의해 Leakage Current는 지수함수적으로 증가합니다. GIDL Current나 Junction Leakage Current가 발생할 경우 Vgs=0V 근처 영역에서 Vgs가 감소함에 따라 급격히 Ioff가 증가합니다. Ioff는 제품의 Stand-by Current를 결정하므로 높을수록 Power 소모가 심하여 Power 소모에 악영향을 미칩니다.

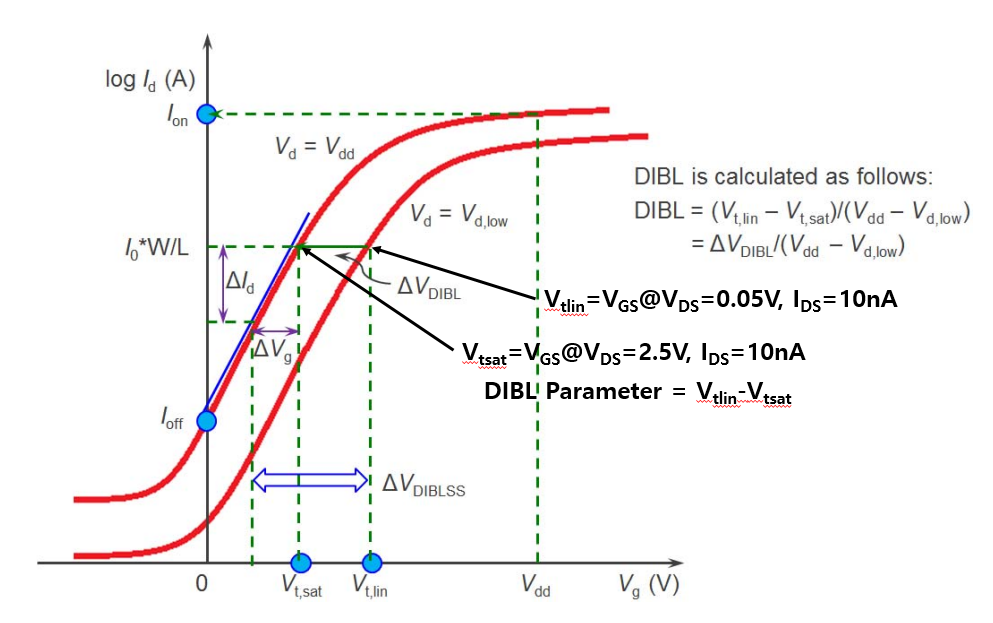

[꼬리 2.6]. DIBL (Drain Induced Barrier Lowering) Parameter 측정 방법에 대해서 설명하세요.

Drain 전압 인가 시 Drain의 Electric Field에 의해 Source와 Channel 영역의 Potential Barrier가 낮아지면서 Threshold Voltage가 감소하는 Vt roll-off 현상을 DIBL이라고 합니다. Drain Voltage에 의해 Threshold Voltage가 감소하는 정도를 나타내는 것이 바로 DIBL Parameter입니다. DIBL Parameter 측정방법은 우선 Vdsat을 구합니다. 이후 Drain에 0.05V를 인가하여 Gate Voltage를 Sweep함으로써 Ids-Vgs Curve 특성을 측정합니다. 이후 Ids=10nA/20um인 Gate 전압이 Vtlin이며, Vtlin-Vtsat을 계산하여 mV 단위로 표현합니다. Short Channel Device에서 DIBL 현상이 심화되며 Channel Length가 짧아짐에 따라 DIBL Parameter가 증가합니다. Lightly Doped Drain, LDD의 농도 증가 시 DIBL Parameter는 증가하며, Halo Doping의 Dopant Dose량이 증가할 경우, DIBL Parameter는 감소합니다.

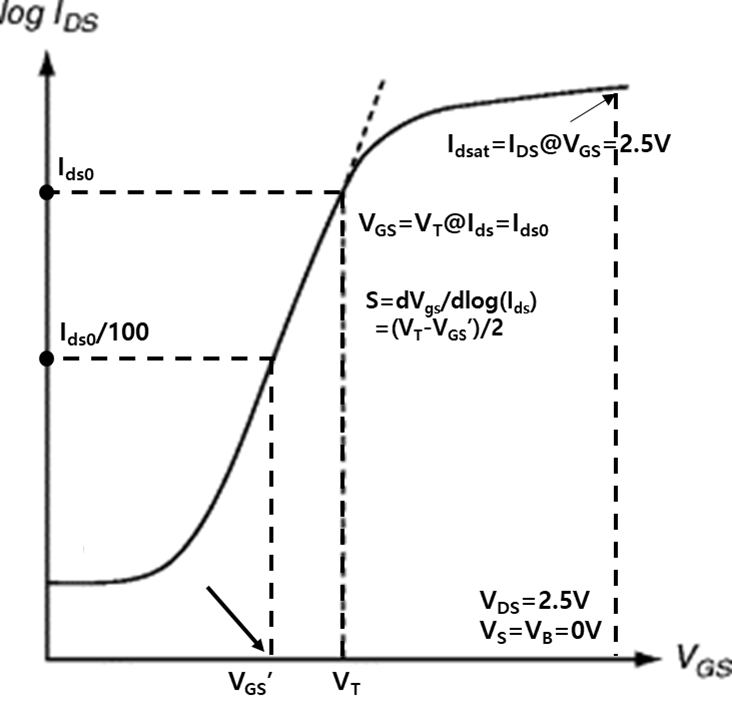

[꼬리 2.7]. Subthreshold Slope (S-factor) 측정 방법에 대해서 설명하세요.

Subthreshold Region에서 Drain Current를 1 Decade (10배) 증가 시키기 위한 Gate Voltage로 정의합니다. 소자가 Switch로서 얼마나 잘 동작하는지에 대한 지표가 되며, Subthreshold Region에서 log(Ids)-Vgs Curve 특성에서 Slope의 역수로 표현합니다. (단위는 mV/decade), S=(dVgs/dlog(Id). S-factor를 측정하는 방법은 우선 Vt 측정 시 Vgs=Vt 일 때의 Ids를 Ids0라 나타내며, Drain에 동작전압을 인가합니다. Source와 Body는 Ground 상태에 놓고, Ids=Ids0/100 인 Gate 전압을 Vgs'으로 표시합니다. 이 때, S=(Vt-Vgs')/2로 계산을 통해 S-factor를 구할 수 있습니다.

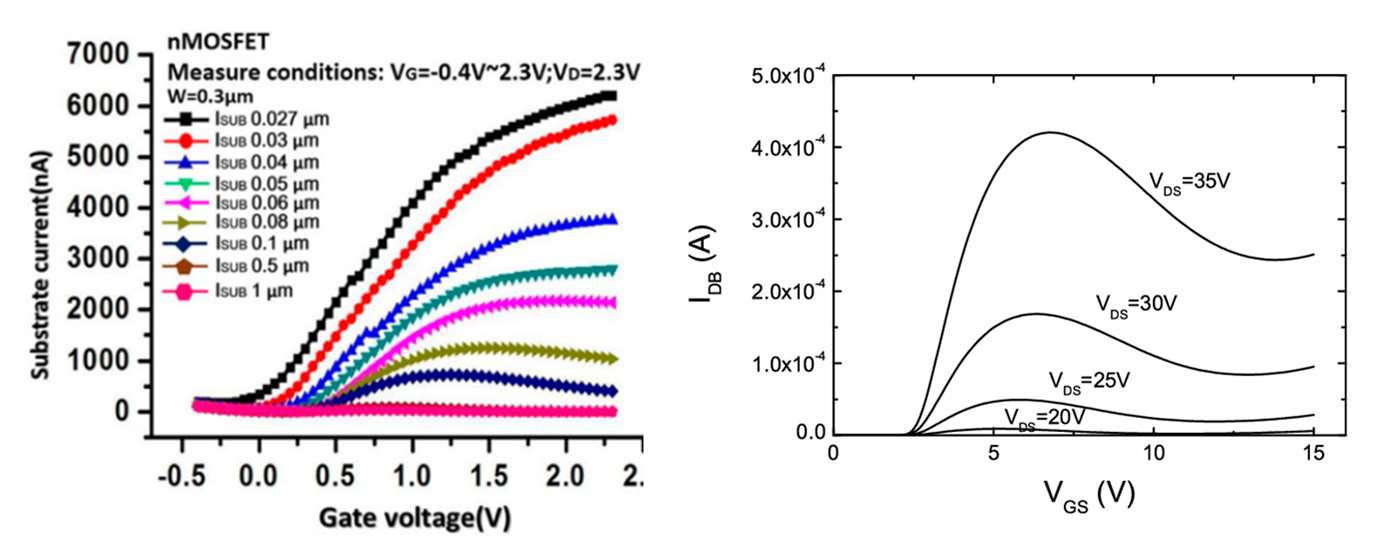

[꼬리 2.8]. Maximum Substrate Current, Isub_max 측정 방법에 대해서 설명하세요.

Drain Bias에 의한 수평 Electric Field에 의해 Channel의 Drain 부근에 발생한 Pinch-off Region 내에서 Impact Ionization에 의해 발생한 EHP의 Hole은 Substrate Leakage, Electron은 Drain Leakage Current를 발생시킵니다. Hot Carrier Injection, HCI에 의한 소자 신뢰성을 결정하는 중요한 Parameter입니다. 'Isub∝Id*S*exp(-Φ/λEm)'. Maximum Substrate Current를 측정하는 방법은 Source와 Body는 Ground 상태에 놓고, Drain에 동작전압을 인가한 후 Gate Voltage를 Sweep 함으로써, Substrate Current, Isub를 측정하여 가장 큰 값이 Isub_max이 됩니다. Substrate Current, Isub는 Gate Voltage에 증가에 따라 대략 Vds/2 이후에 감소합니다. Isub는 Drain Current에 비례하며, Ids는 Vgs가 증가함에 따라 증가합니다. 수평 전계인 Em은 Vgs가 증가함에 따라 감소하므로 이러한 현상이 발생하는 것입니다. Substrate Current는 Channel Length가 짧아짐에 따라 증가하며 PMOS보다 NMOS에서 더 큰 Substrate Current가 발생합니다.

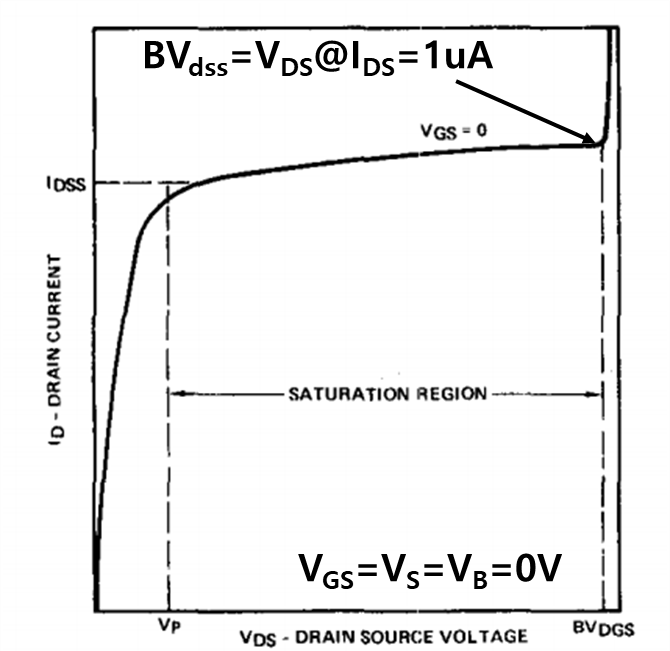

[꼬리 2.9]. Drain-to-Source Breakdown Voltage, BVdss 측정 방법에 대해서 설명하세요.

Gate Voltage를 인가하지 않은 상태. 즉, Interface에 Channel이 형성되지 않았을 때의 Breakdown Voltage로, Junction Breakdown이나 Punch Through에 의해 결정됩니다. Drain-to-Source Breakdown Voltage는 Source와 Body를 Ground 상태에 놓고, Drain 전압을 Sweep 하면서 Ids가 1uA/20um인 Vds가 BVdss 입니다. Long Channel Device의 경우 Junction Breakdown이 주 원인이고, Short Channel Device에서는 Punch Through 현상이 주 원인으로 Channel Length가 짧아지면서 특정 임계 Channel Length에서 급격히 감소하여 소자의 Margin을 결정하는 핵심 Parameter입니다.

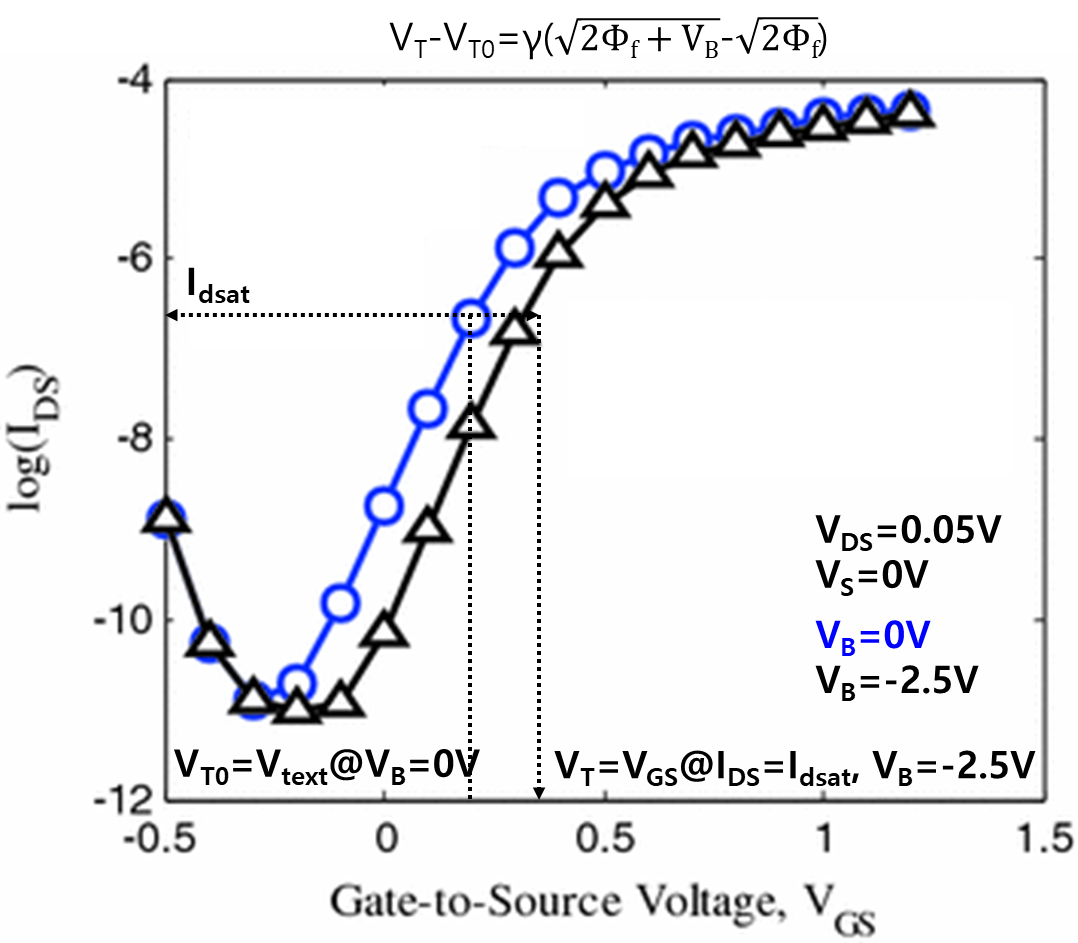

[꼬리 2.10]. Body Factor, γ 측정 방법에 대해서 설명하세요.

Body Effect는 Substrate Bias에 의해 Threshold Voltage가 변하는 특성입니다. Back Bias에 의한 Threshold Voltage 변화의 Sensitivity를 결정하는 Parameter가 바로 Body Factor입니다. Body Factor를 측정하는 방법은 Body Bias, Vb=0V에서 Vt를 측정하고, Vgs=Vt에서 Idsat을 추출합니다. 이후, Vb=Vds/2, 동작전압의 절반의 Bias를 Body Bias로 인가한 후에, Vds=0.05V에서 Gate Voltage를 Sweep 하여, Idsat이 흐르는 Vgs가 Vt'. 2Φf=0.7V로 계산하여, Vth-Vt0=γ((2Φf+Vb)^1/2-Φf^1/2) 식에서 Body Factor, γ를 얻을 수 있습니다. Back Bias는 NMOS는 Negative Bias, PMOS는 Positive Bias를 인가합니다. Back Bias가 증가하면 Vt 또한 증가하며, Doping 농도가 감소 또는 Oxide Thickness, Tox가 감소할 경우 Body Factor 또한 감소합니다.

[PCM 측정 정리]

반도체 공정을 진행한 Wafer에 형성되는 각종 소자(Tr., 저항, 다이오드, Capacitor 등)의 전기적 특성을 측정하여 공정 진행 상태를 판단할 수 있는 DC Parameter를 추출하는 과정을 PCM Parameter 측정이라고 합니다.

① Wafer 상태에서의 측정 위치

-8인치 : Wafer 내의 Top, Center, Bottom, Left, Right 5 Point 측정

-12인치 : Wafer 내의 Top, Center, Bottom, Left, Right 9 point 측정

② PCM 측정 주기

- All Wafer 에 대하여 측정하는 전수검사 실시. 5 or 9 point/Wafer

③ PCM 측정 항목

-Threshold Voltage (Vth) : MOSFET의 Channel이 형성되는 Gate 전압 Vgs, 즉, Si 표면의 Minority Carrier Density가 Bulk의 Carrier Density와 같아지는 Strong Inversion이 일어나는 전압을 측정

-Saturation Drain Current (Idsat) : Drain과 Gate에 동작전압 인가시 Drain Current로 Vth와 함께 소자의 특성을 결정하는 주요 Parameter이며 회로의 Performance를 결정함

-Leakage Current (Ioff) : Channel이 형성되기 이전에 흐르는 Current로 Drain과 Bulk, Source 간의 Diffusion Current

-Drain-to-Source Breakdown Voltage (BVdss) : Gate에 전압이 인가하지 않았을 때, 즉 Channel이 형성되지 않았을 때의 Breakdown Voltage로 Junction Breakdown이나 Punch Through에 의해 결정됨

-Sheet Resistance : Active, Poly 그리고 Metal Layer의 면저항을 평가.

-Contact 및 Via Resistance : 회로 배선에서는 여러 층의 Metal Layer를 사용하여야 하며, 이들 Metal 배선들은 Contact / Via를 통하여 서로 연결되므로 Contact / Via의 정상적인 연결 여부에 대한 평가

-Diode, Capacitor 등 공정 Parameter에 대하여 PCM 측정.

오늘은 Process Control Monitor, PCM Parameter와 측정 방법에 대해서 알아보았습니다.

즐거운 주말 되세요!

반응형

그리드형(광고전용)

'반도체사관학교 훈련과정 > 반도체 전공정' 카테고리의 다른 글

| [포토 공정] Photo Lithography 공정, 불량 사례 (0) | 2022.03.28 |

|---|---|

| [반도체 공정] Process Control Monitor, PCM Parameter 총정리 [2/2] (0) | 2022.03.26 |

| [식각공정] 훈련 2 : "Etching (식각) 공정에 대해서 설명해주세요" (18) | 2022.03.11 |

| [반도체 수율] "수율 개선을 위한 공정제어기술" (0) | 2022.03.07 |

| [반도체 수율] "수율이 중요하다는데 도대체 수율이 뭘까?" (0) | 2022.03.07 |

최근댓글