반응형

SDC file (Synopsys Design Constraints)

SDC 파일은 Synopsys Design Constraints 혹은 Static Timing Constraints (STA)라고 하죠. STA는 특히 SDC 파일 내에서설정하는 구체적인 타이밍 제약 조건을 의미합니다. 이는 디지털 회로 설계에서 Timing 분석을 위해 필요한 다양한 제약 조건들에 대한 정보가 포함되어 있습니다. SDC 파일 내 제약 조건은 Clock 주기, 입력 및 출력 지연, 그리고 Data 경로 지연과 같은 Timing에 대한 요구사항을 명시합니다. 정확한 Timing 분석을 위해 EDA Tool이 설계를 분석하고 최적화 하는 데 필요한 정보를 제공함으로써 Timing 문제가 발생하는 것을 방지하죠. 뿐만 아니라, 공정 상의 특성을 반영하여, 공정과 관련된 특정 제약 사항 또한 포함합니다.

- Clock 정의 : 'create_clock' 명령어를 사용하여 Clock 주기와 관련 정보를 정의함.

- Port 제약 조건 : 'set_input_delay' 및 'set_output_delay' 명령어를 통해 입출력 지연을 설정함.

- 경로 제약 조건 : 특정 경로에서 허용되는 최대 및 최소 지연 정의

- 타이밍 예외 설정 : 특정 조건에서 타이밍 분석을 무시하거나, 다르게 처리할 경우, 'set_false_path' or 'set_max_transitions' 등 사용함.

- SDC 파일은 주로 타이밍 분석 도구 (Synopsys Prime Time / Cadence Tempus)에 사용됨.

설계 검토 과정에서 SDC 파일을 활용하여 타이밍 요구사항이 충족됐는지 확인할 수 있고, SDC 파일의 구성과 작성 방법을 잘 이해하고 적용한다면, 보다 안정적이고 성능 높은 디지털 회로 설계를 할 수 있죠. - SDC 파일은 Synopsys 환경에서 Static Timing 제약을 작성하고 관리하는데 있어서 중요한 Data입니다. SDC 파일을 통해 설계 엔지니어는 회로의 성능을 최적화하고 원하는 Timing을 Targeting 해야겠죠.

- .sdc file은 Synopsys Design Constraints : Synopsys에서 정의한 설계 제약 조건 파일 Format임.

- SDC는 설계를 제약하는 일반적인 형식이며, 거의 모든 Synthesis 및 PnR tool에 지원되며, (다양한 EDA 도구에서 사용할 수 있는 표준임!!) SDC 파일에는 Timing, Area, Power Constraints 조건들이 포함됩니다.

- SDC의 Syntax는 TCL Format을 기반으로 모든 명령어는 TCL 프로그래밍 언어의 문법을 따르죠.

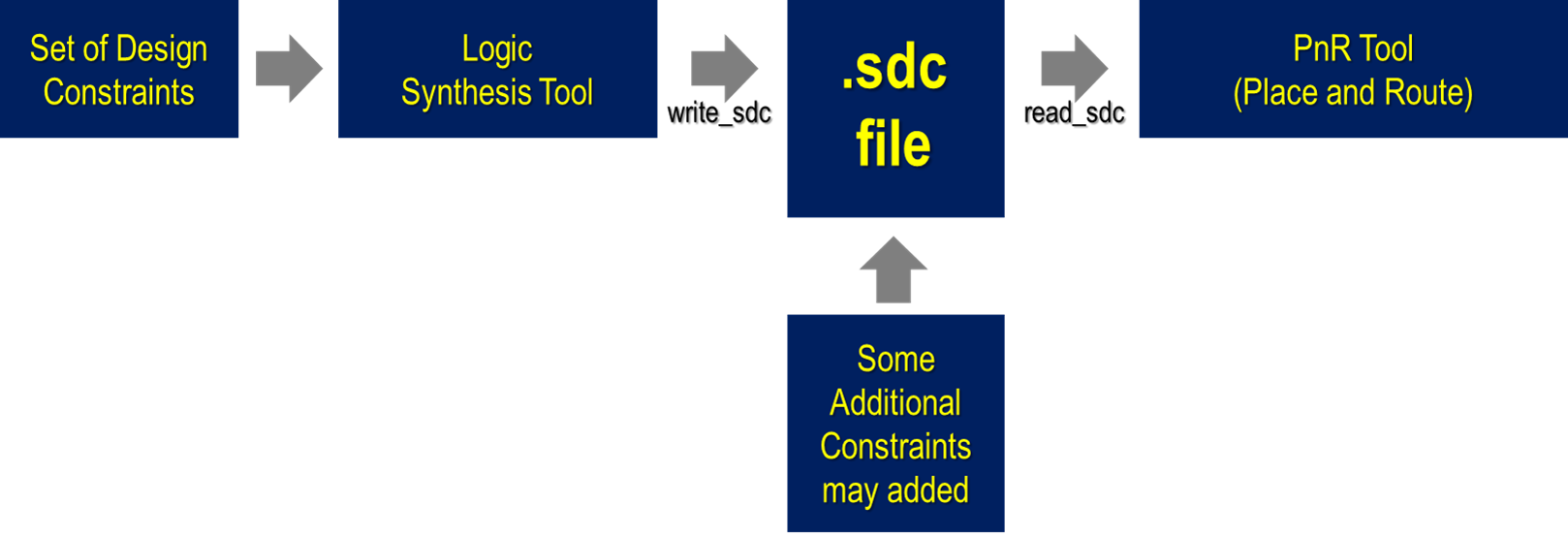

"#" 한 줄 주석 추가, 명령이 길어질 떄는 "로 줄을 바꿈. - PnR을 할 때는, 설계 제약 조건을 SDC 파일을 Input File로 사용합니다. 이러한 sdc 파일은 Synthesis Tool에서 생성할 수 있죠ㅎ. "write_sdc' 명령어로 SDC 파일을 생성하고, 'read_sdc' 명령어로 SDC 파일을 불러올 수 있죠.

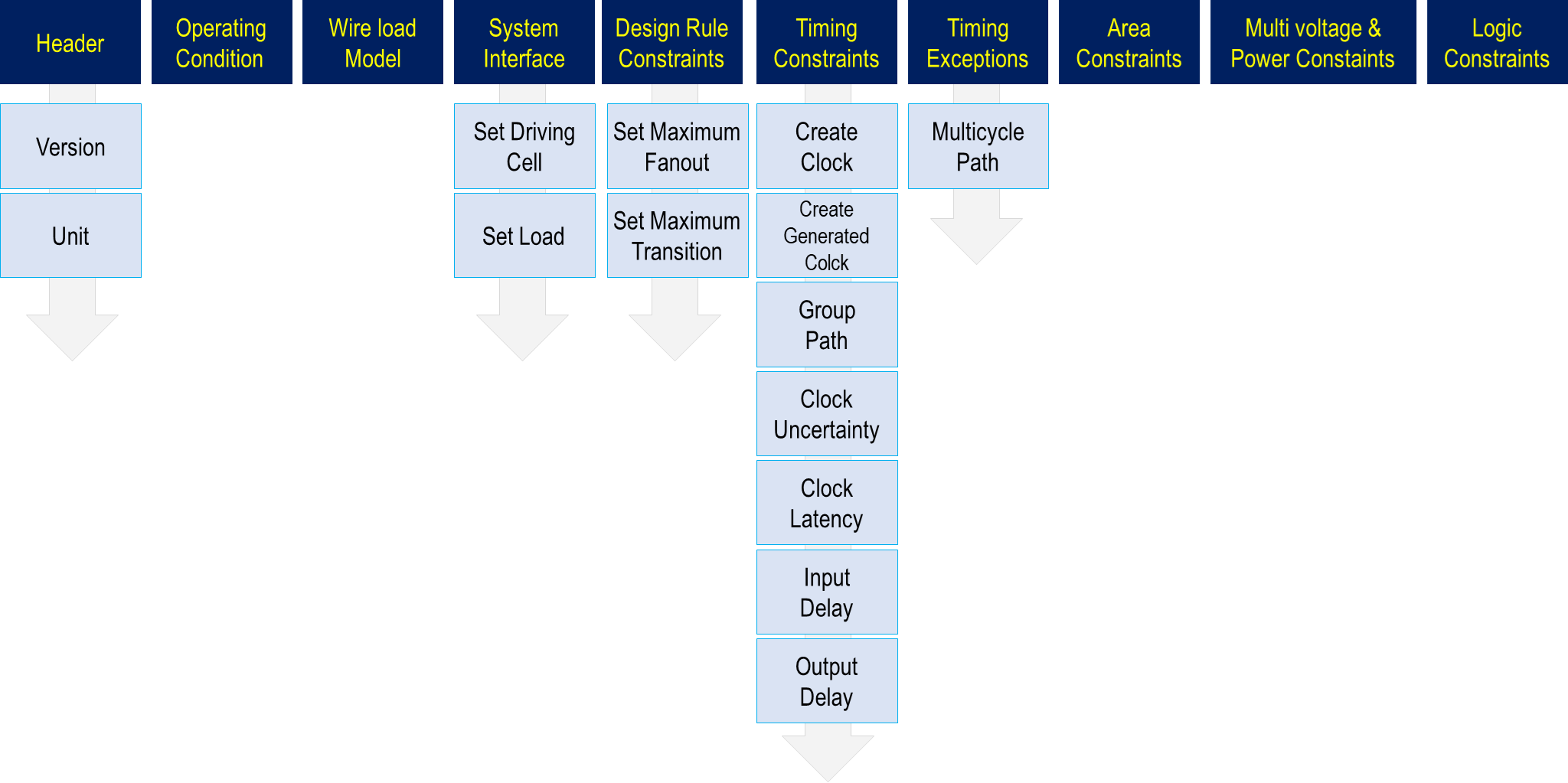

Header

- 1. SDC Version

-. .sdc file 내 version 정보입니다. 1.9, 2.0, 2.1 과 같이 표현되죠.

-. ex) set sdc_version 2.0 - 2. Units

-. 'set_unit' 명령은 .sdc file의 unit을 정의합니다. Time, Resistance, Capacitance, Voltage, Current, Power 등 Unit을 Define 합니다.

-. ex) set_units -time ns -resistance Kohm -capacitance pF -voltage V -current mA

System Interface

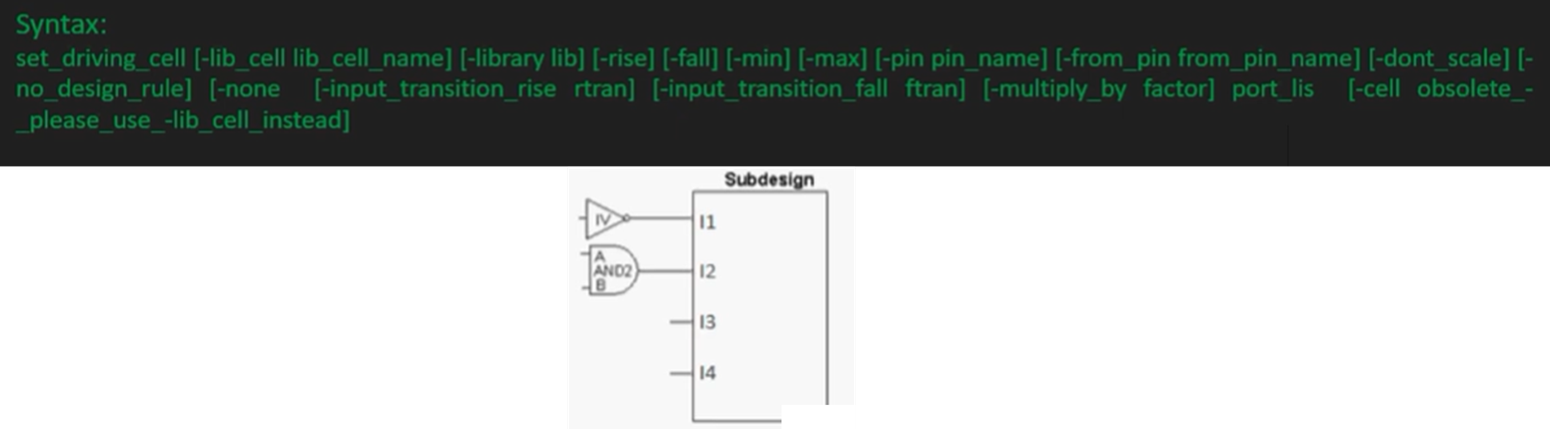

- 3. Set Driving Cells.

-. input or inout ports에서 Tech Library의 Cell에 의해 구동되는 구동 특성을 정의합니다. Input Ports를 가지는 Library Pin들의 정보를 기반으로 Delay 계산을 정확하게 Modeling 할 수 있습니다. 즉, 특정 명령어가 Input Port 구동 특성을 정의하고, 이를 통해 Technology Library의 Pin과 연결하여 더 정밀한 Timing 계산이 가능하다는 것입니다.

-. Example :

-. set_driving_cell -lib_cell IV {I1}

-. set_driving_cell -lib AND2 -pin Z -from_pin B {I2}

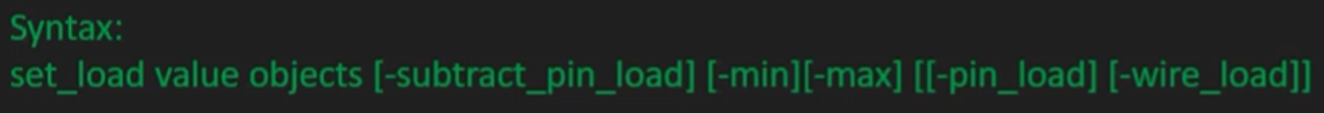

- 4. Set Load

-. Set Load 명령은 설계에서 지정된 Port와 Nets 간에 부하 특성을 설정하는 기능을 합니다. 부하 값의 단위는 SDC 파일의 Unit Section에서 정의된 Capacitance 단위가 되죠. 즉, 특정 명령어가 현재 설계 내 Port와 Nets 부하 특성을 설정합니다.

-. Example : set_load -pin_load 0.001 [get_ports {port[10]}]

Design Constraints

- 5. Maximum Transition

-. Maximum Transition 명령은 지정된 Clock, Port, 또는 설계 내 Maximum Transition Time을 설정하는 Design Rule Constraints 제약을 설정합니다.

-. Example : set_max_transition 2.5 [get_ports IN]

- 6. Set Maximum Fanout

-. 설계 혹은 지정된 Port에 대한 maximum fanout load를 설정함.

-. Example : set_max_fanout 5 [get_ports {port(10)}]

Timing Constraints

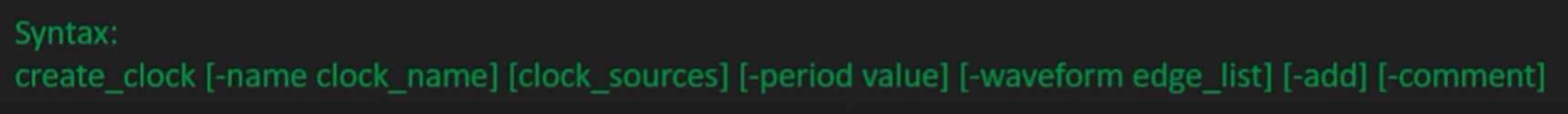

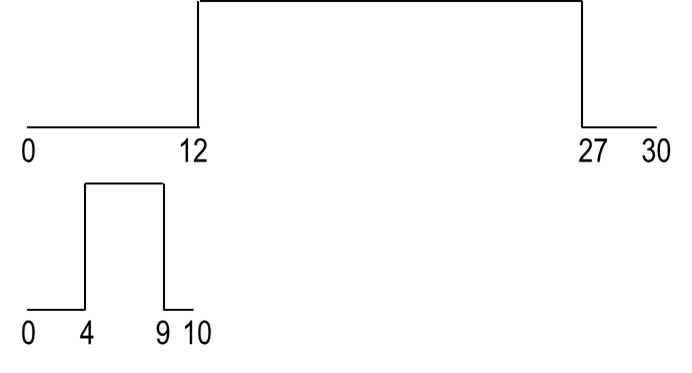

- 7. Create Clock

-. 'create_clock' 명령은 현재 설계에서 Clock 객체를 생성합니다.

-. 지정된 source_objects들은 현재 설계에서 Clock Source로 정의되고, Port나 Pin은 단일 Clock Source가 될 수 있습니다. Source_objects으로 지정되지 않고, clock_name만 정해지면, 가상 Clock이 생성됩니다.

-. Example :

create_clock "u13/Z" -name "CLK" -period 30 -waveform {12.0 27.0}

create_clock -name "PHI2" -period 10 -waveform {0.0 5.0}

create_clock -name "clk2" -period 10 -waveform {0.0 2.0 4.0 6.0} {clkgen1/Z clkgen2/Z clkgen3/Z}

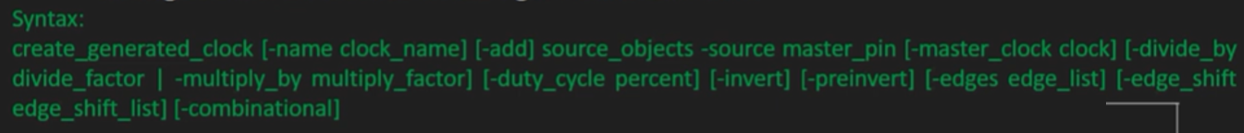

- 8. Create Generated Clock

-. 'create_generated_clock' 명령은 생성된 Clock의 객체를 생성하는 명령입니다. 특정조건에 따라 만들어진 Clock을 정의합니다. 또한 Pin이나 Port를 생성된 Clock 객체 (Clock Source)로 지정할 수 있습니다.

-. Master Clock이 변경될 때마다 생성된 Clock 역시 자동으로 변경됩니다. Mask Clock과 연관된 모든 Clock이 자동으로 Update 되는 기능이 있죠.

-. 생성된 Clock은 Frequency를 나눈 Clock, 혹은 곱한 Clock, 또는 Edge를 유도한 Clock, 반전 Clock도 생성할 수 있습니다. 즉, 생성된 Clock을 다양한 형태로설정 할 수 있으며, Frequency를 조절하거나 Signal Edge를 기반으로 설정할 수 있습니다.

-. Exampe : create_generated_clock -multiply_by 3 -source CLK [get_pins div3/Q]

-. 예제는 CLK라는 Source Clock으로 Clock을 생성하며, 생성된 Clock의 Frequency는 CLK Clock의 3배 입니다. 따라서 Period는 1/3이 되죠.

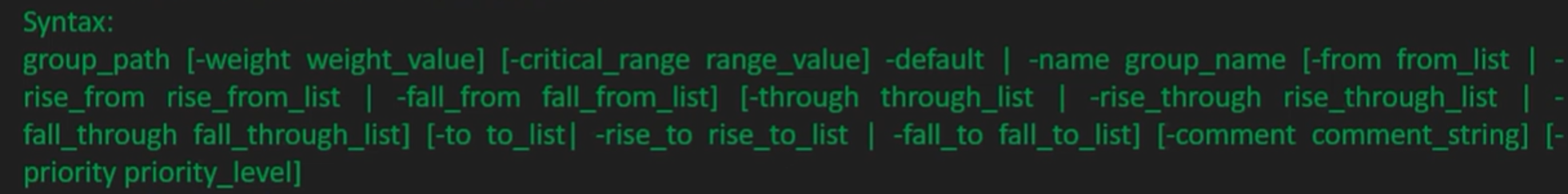

- 9. Group Path

-. 'group_path' 명령은 경로 또는 Endpoints Sets을 Cost Function 계산을 위해 Grouping 하는 기능을 합니다. Group을 사용하면 다른 Group에서 더 큰 Violation이 있을 수 있지만, 최적화 할 경로 집합을 지정할 수 있죠. 특정 Group 내에서의 최적화도 가능하게 하며, 다른 Group에서 문제가 발생했을 때, 그 영향을 미치지 않도록 설정할 수 있죠.

-. Endpoint가 지정되면, 해당 Endpoint로 연결되는 모든 경로가 그룹화 됩니다. 특정 Endpoint로 향하는 모든 경로가 동일 그룹으로 묶인다는 것이죠.

-. 'from_list' 또는 'to_list'에 Clock이 지정되면, 해당 Clock과 관련된 모든 Endpoint가 그룹에 포함됩니다. 하나의 Clock이 List에 포함되면, 이 Clock과 연관된 모든 Endpoint가 Group에 추가되죠.

-. 'create_clock' 명령은 새로운 Clock에 대해 자동으로 그룹을 생성하고, 가중치를 1.0로 설정하며 Clock name과 동일하게 명명되죠.

-. Example :

group_path -name "group1" -weight 2.0 -to {CLK1A CLK1B}

group_path -name GROUP1 -from [get_ports ABC/in3] -to [get_ports FF1/D]

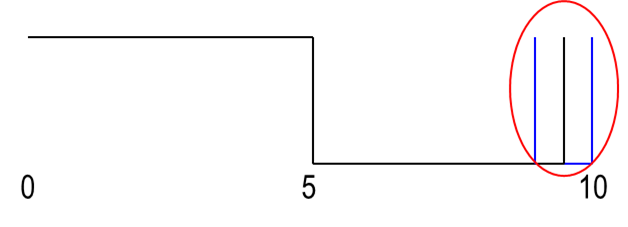

- 10. Clock Uncertainty

-. Clock을 정의한 후에, Clock network의 Variance를 처리하기 위해서 Clock Uncertainty를 추가해야 합니다. Clock Uncertainty는 Clock Network와 Clock Source 자체의 비이상적인 특성으로 인해 발생하는데, Clock Network의 Variance를 감안하여 System에 Error에 대한 Margin을 확보해야 합니다.

-. 'set_clock_uncertainty' 명령은 Interclock uncertainty 또는 Simple uncertainty 두 가지 유형의 Clock 불확실성을 설정할 수 있죠.

-. Endpoints에 예상되는 최악의 왜곡 (Worst Skew)나 Clock Domain 간의 Skew를 설정하고 이 설정값을 증가시켜 Setup / Hold에 대한 추가 Margin을 고려한 설계를 할 수 있습니다.

-. Example : 아래 명령은 Clock Uncertainty 0.2ns를 Clock Edge 각 Side에 추가하는 예제입니다.

set_clock_uncertainty -setup 0.5 [get_clock clk1]

set_clock_uncertainty -hold 0.5 [get_clock clk1]

-. Example : 또한 해당 명령어를 통해 Clock의 rise and fall time에 대한 불확실성도 추가할 수 있죠.

set_clock_uncertainty -max_rise 0.12 [get_clock clk1]

set_clock_uncertainty -max_fall 0.12 [get_clock clk1]

set_clock_uncertainty -min_rise 0.12 [get_clock_clk1]

set_clock_uncertainty -min_fall 0.12 [get_clock_clk2]

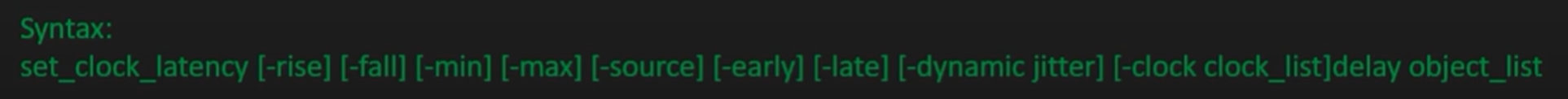

- 11. Clock Latency

-. 클록 지연(Clock Latency)는 Clock 신호가 Sequential Device의 Clock Pin에 도달하는 데 걸린 지연 시간을 지정합니다. Clock 신호가 특정 Device에 도착하는데 필요한 지연 시간이죠.

-. Clock Latency에는 두 가지 유형이 있습니다. ① 네트워크 지연 (Network Latency, default), ② 소스 지연 (Source Latency, -source option 사용 시)

-. Clock Network Latency의 경우 Clock 정의 지점 (create_clock 명령을 통해 정의된)에서 Register의 Clock Pin까지 Clock 신호가 도달하는 데 걸리는 시간입니다.

-. Clock Source Latency의 경우, Insertion delay (삽입 지연)이라고도 불리며, Clock 신호가 실제 이상 파형의 Origin 지점에서 설계 내 Clock 정의 지점까지 도달하는 데 걸리는 시간이죠. (참 어렵죠...?) 쉽게 이야기 하면, Clock 신호가 발생하는 실제 위치에서 설계 내부에 Clock이 정의된 위치까지 Clock 신호가 전달되는 데 필요한 지연 시간이죠.

-. Example : set_clock_latency 2.35 [get_pins ABC/XYZ/CP]

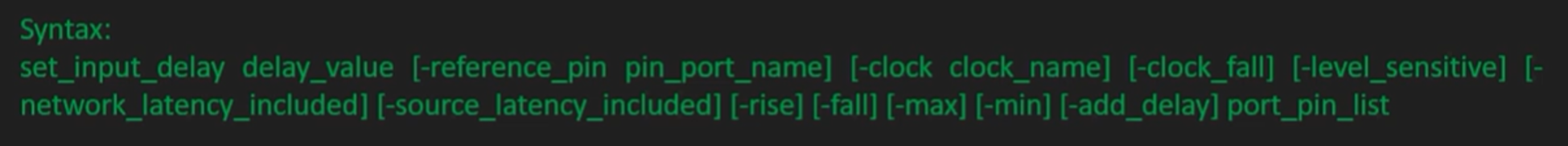

- 12. Input Delay

-. Input Port의 Timing 요구사항을 Clock Edge에 대해 정의합니다. 입력 Port는 지정되지 않는 한 Input Delay이 0으로 가정됩니다. 입력 포트는 기본적으로 Clcok의 변곡점에 대한 지연이 없다고 가정하며, 필요한 경우 이를 설정할 수 있죠.

-. 지정해야 할 delay_value는 시작 지점과 set_input_delay가 설정되는 객체 간의 지연이며, Clock Edge를 기준으로 한 상대적인 지연 시간을 의미하죠.

-. Example : set_input_delay -max 1.35 -clock clk1 {ain, bin}

- 13. Output Delay

-. set_output_delay 명령은 Output port의 출력 경로 지연을 Clock Edge를 기준으로 상대적으로 설정합니다. 출력 Port 역시 지정되지 않는 한 Output Delay는 없다고가정하죠.

-. Example : 아래 명령은 CLK1의 Positive Edge (Default)와 관련하여 모든 출력 Port의 Output Delay를 1.7 단위로 설정합니다.

set_output_delay 1.7 -clock [get_clocks CLK1] [all_outputs]

-. Example : 아래 명령은 -max 값은 가장 긴 경로를 나타내며, -min 값은 가장 짧으 경로를 나타내죠. -max와 -min이 별도로 지정되지 않으면, 최대 및 최소 Output delay는 동일한 것으로 가정됩니다.

set_output_delay -max 1.4 -clock {CLK} [get_ports {Y}]

set_output_delay -max 1.0 -clock {CLK} [get_ports {Y}]

Timing Exception

- 14. Multicycle Paths

-. Muliticycle Path는 Default인 Signle Cycle Timing 요구사항 경로에 대한 Timing Exception 이죠. 즉, Multicycle Path는 Single Cycle timing 요구사항에 벗어난 경우를 의미합니다.

-. Multicycle Path에서 신호는 경로의 Start point에서 Endpoint까지 전달되는 데 하나 이상의 단일 Clock Cycle이 반드시 필요합니다. 즉, 신호가 경로의 시작점에서 끝지점까지 전달되는 데 있어 여러 Cycle들이 소요될 수 있음을 말하죠.

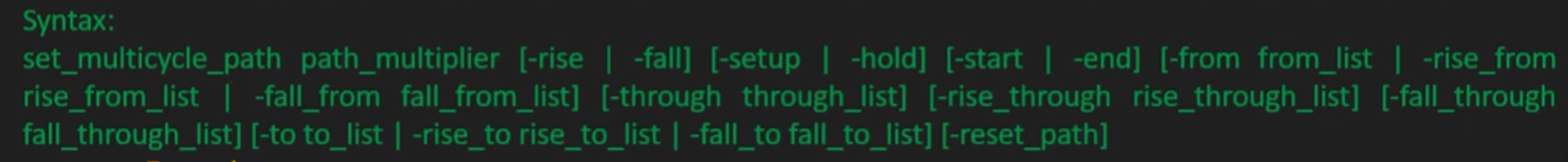

-. 'set_multicycle_path' 명령은 Setup & Hold Check을 위해 Data 경로가 가져야 하는 Cycle 수를 지정합니다.

-. dd

-. Example : 아래 명령을 통해 A에서 B까지이 경로가 2 Cycle로 설정되도록 제약 조건을 정의한 것이죠.

set_multicycle_path 2 -from A -to B

set_multicycle_path 3 -from C

-. Source와 End 사이에 -through point를 통해 추가적인 경로를 세부적으로 정의할 수 있으며, 이는 Source Point만 선언한다면 모든 경로에 대해 Multicycle 경로를 설정할 수 있다는 것이죠.

- 15. False Paths

-. False path는 신호를 전달할 수 없는 경로입니다. 예를 들어, 어떤 입력 조합으로도 활성회 되지 않는 경로가 바로 False Path이죠. 다시 말하면, False Path는 신호가 흐르지 않는 경로를 의미하며, 실제로 사용되지 않는 경로입니다.

-. 이러한 False Path는 'set_false_path' 명령을 사용하여 비활성화 시킬 수 있습니다. 그렇게 되면 해당 경로는 Timing Analysis 대상에서 제외됩니다.

-. Example :

set_false_path -from U1/G -to U1/D

set_false_path -from {ff12} -to {ff34}

여러분들 오늘은 반도체 설계에서 정말 중요한 Timing Analysis을 위한 SDC 파일에 대해서 알아보았습니다. 이러한 모든 파일은 공정 개발 후 Fab에서 설계 엔지니어들이 IC에 대해 분석을 할 수 있도록 Data File을 제공해야죠. 참으로 공부할 게 많죠ㅎㅎ.

반응형

그리드형(광고전용)

최근댓글