오늘은 DRAM의 성능을 향상시키기 위한 DRAM 기술의 변천사와 차세대 DRAM에 대해서 알아보도록 하겠습니다.

[질문 1]. 고대역폭 메모리 HBM에 대해서 설명해보세요.

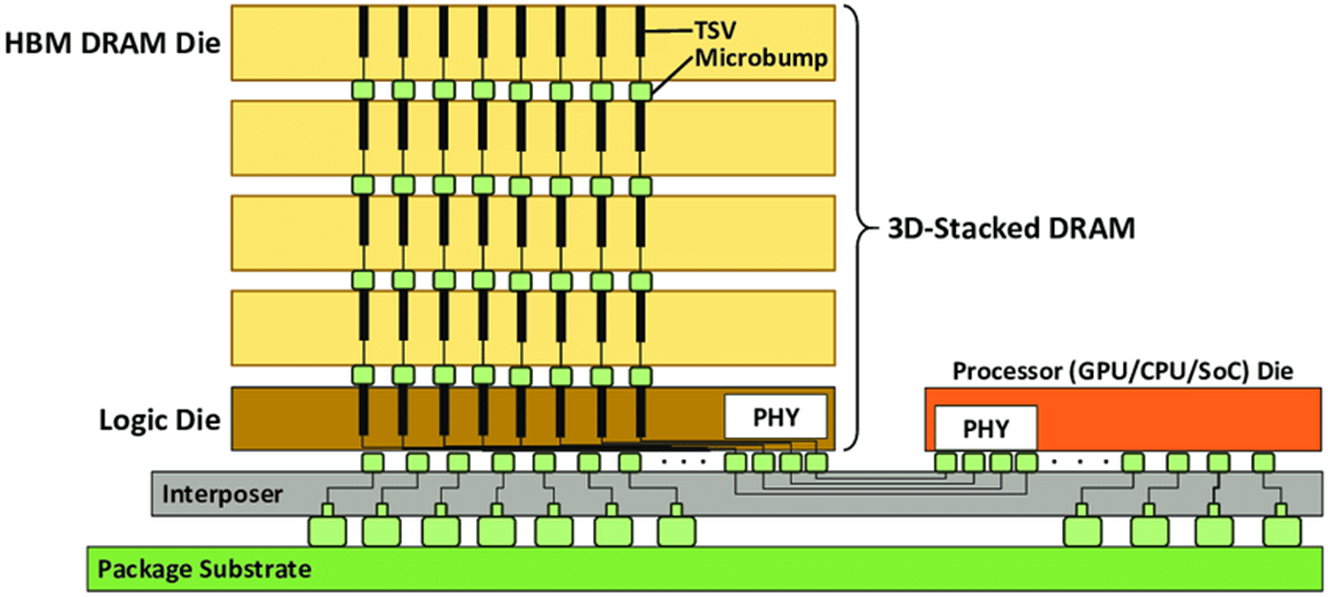

DRAM은 셀의 고집적화 되면서 Re-fresh 과정에서 주변 셀의 공백으로 인해 CPU의 정보를 전달하는 데이터 전달 속도에 부정적인 영향을 미치게 됩니다. 이를 극복하기 위해서 고안된 방법이 바로 High bandwidth memory, 고대역폭 메모리 HBM 기술입니다. 한 개 칩에 패키징 기술로 4층 이상의 DRAM 다이를 적층시킴으로써 집적도를 늘리는 기술입니다. 셀 영역에서 Re-fresh로 인한 주변 셀의 공백 현상이 발생하더라도, 이를 대체할 수 있는 '셀'이 늘어나면서 데이터 처리량, 즉 대역폭을 크게 증가시킬 수 있습니다.

[질문 2]. 미세화에 따른 DRAM Cell의 영향에 대해서 설명해주세요.

DRAM의 셀 크기는 점점 미세화되고 있습니다. 미세화에 따라 DRAM의 고집적도를 달성함으로써 고용량의 데이터를 저장할 수 있고, 저전력 동작이 가능하게 됩니다. 최근 이슈에 따른 기존 파운드리 시스템반도체에서만 적용되었던 EUV 극자외선 공정을 메모리 공정에도 도입한다는 기사를 보았습니다. 그만큼 미세화 공정은 DRAM 경쟁력을 갖추는데 반드시 풀어야 할 과제라고 생각합니다. 소자 Dimension이 작아지면서 short channel effect가 발생하게 됩니다. 그에 따라 기생 capacitance 성분이 증가하면서 threshold voltage, Vt에 악영향을 미치게 되고 게이트 구동력이 저하됩니다. 그에따라 subthreshold current가 증가하게 되면서 소자 성능과 신뢰성이 저하되는 이슈가 발생합니다. 특히, 전하의 누설로 인해 DRAM의 capacitor에 저장된 정보가 손실되거나 발열이 발생하여 소자가 열화되는 이슈가 발생할 수 있습니다.

"메모리 초격차" 삼성, EUV 공정으로 만든 14나노 D램 양산

삼성전자가 극자외선 EUV 공정기술을 적용하여 업계 최소 선폭인 14나노 DRAM 양산을 시작했다고 발표했습니다. 그동안 15nm 공정으로 DRAM을 양산해왔으며 '하반기에는 14nm DRAM 5개 layers에 EUV 공정을 적용할 것' 이라고 발표했습니다. 14나노 DRAM에 EUV 공정을 적용하면 원가 경쟁력 확보와 성능향상을 달성할 수 있습니다.

EUV 공정이 적용된 삼성전자 D램은 업계 최고의 웨이퍼 집적도를 지닙니다. 이전 세대 대비 생산성이 약 20% 향상됐습니다. 또한 소비전력은 이전 공전 대비 20% 개선됐고, 이번 신규 공정은 최신 DDR5 DRAM에 먼저 적용할 것으로 발표했습니다. 최신 DDR5 DRAM은 이전 DDR4 대비 속도가 2배 이상 빠르고 저전압으로 동작합니다.

출처 : 중앙일보

메모리 초격차…삼성, EUV 공정으로 만든 14나노 D램 양산

한진만 삼성전자 메모리사업부 부사장은 "14나노 D램에 EUV를 적용해 원가 경쟁력을 확보할 수 있을 것으로 본다"고 자신했다. 삼성전자에 따르면 EUV 공정이 적용된 삼성전자 14나노 D램은 업계 최

www.joongang.co.kr

[꼬리 2-1]. 미세화에 따른 DRAM 이슈의 솔루션은 어떤 방향으로 진행되고 있는지 설명하세요.

DRAM의 Short channel effect, SCE에 따른 누설전류를 억제하기 위해서 고안된 방법은 바로 셀 구조의 변화입니다. 기존 planar 구조의 트랜지스터는 gate 폭이 줄어들면서 SCE 효과가 극대화 됐고, 채널 길이가 짧아지면서 누설전류에 의해 전자가 대거 탈출하는 이슈가 발생했습니다. 이러한 이슈를 개선하기 위해서 Recessed Channel Array Transistor, RCAT 그리고 Buried CAT과 같이 소자의 구조의 변화를 줌으로써 SCE를 억제하고 있습니다.

[꼬리 2-2]. Recessed Channel Array Transistor, RCAT에 대해서 설명하세요.

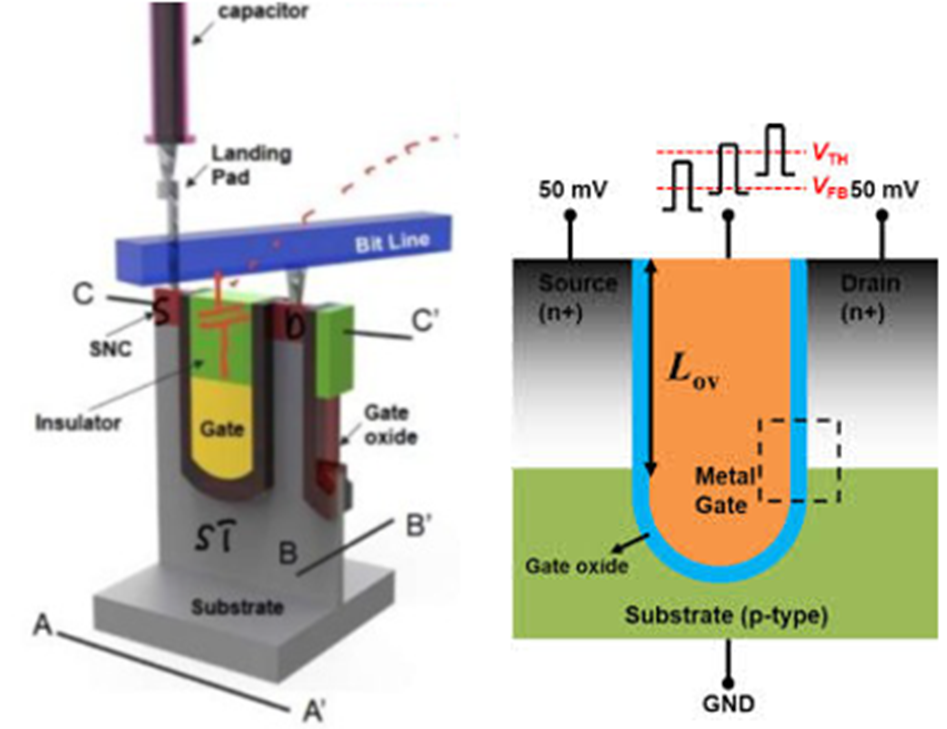

RCAT은 Recessed Channel Array Transistor로 'Recessed'는 기존의 planar한 채널 모양을 'U' 자형으로 오목하게 형성한다는 의미입니다. 기판 방향으로 오목하게 채널을 형성하면서 gate length는 줄었지만 전체 channel length는 길어지게 되면서 short channel effect를 효과적으로 억제할 수 있게 됩니다. 그외에도 RCAT의 파생기술로 channel length를 더욱 확장시키기 위해 sphere 구 형태로 제조하는 S-RCAT 기술이 있습니다. transistor를 3차원으로 구현하는 기술이기에, Cell 내부의 transistor를 축소할 수 있고, refresh 능력을 향상시킬 수 있습니다.

[꼬리 2-3]. Buried Channel Array Transistor, BCAT에 대해서 설명하세요.

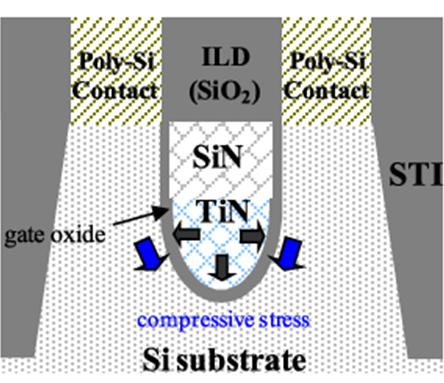

BCAT은 Buried Channel Array Transistor는 게이트를 Buried 아예 묻어버리는 방법을 고안합니다. 그 이유는 channel length를 향상시켰지만 캐리어들이 gate를 통과해 셀 밖으로 누설되는 이슈가 발생했기 때문입니다. 이를 개선하기 위해 RCAT과 달리 gate를 'U'자형 하단에만 위치시키고 그 위에 산화막을 증착시켜 전기적으로 단절시키는 방법입니다. 이 기술을 적용하면 Capacitor와 word line이 멀어지면서 capacitor에 저장된 전하들이 gate로 누설되는 path를 차단할 수 있습니다. 그리고 기존보다 bit line과 word line의 간격이 멀어지면서 배선간 short 이슈를 해결할 수 있습니다.

[꼬리 2-4]. RCAT, DCAT의 이슈에 대해서 설명해주실래요.

"DRAM의 개발 변천사를 보면 RCAT, DCAT 그리고 FinFET 출현, 눈부신 발전이 이루어졌습니다. FinFET과 그리고 그 이후에 nanosheet multi channel FET은 소자 카테고리에 교육을 참고하시길 바랍니다. 이번 장에서는 소자의 이슈와 개선사항에 초점을 맞추어 교육에 임하시길 바랍니다"

RCAT, DCAT 모두 short channel effect를 개선하기 위해서 구조의 변화를 통해 channel length를 증가시키는 방법입니다. gate length는 짧게 유지할 수 있기 때문에 높은 집적도 구현이 가능하게 됩니다. 하지만 channel length가 증가하게 되면서 channel 저항이 증가하고 캐리어의 이동속도가 저하됩니다. 캐리어의 이동은 곧 Drain current 성능과 직결되므로 성능 향상에 있어서 한계에 봉착하게 됩니다. 그래서 도입된 것이 바로 3D 구조의 FinFET입니다. Fin 구조를 형성하여 3면을 gate로 감쌈으로써 채널이 짧아지면서 생기는 gate 구동력 저하 이슈를 획기적으로 개선시키고, short channel을 유지하면서 3면으로 channel width가 확장되어 출력특성이 크게 향상됩니다.

[질문 3]. DRAM의 Capacitor의 변화에 대해서 설명해주세요.

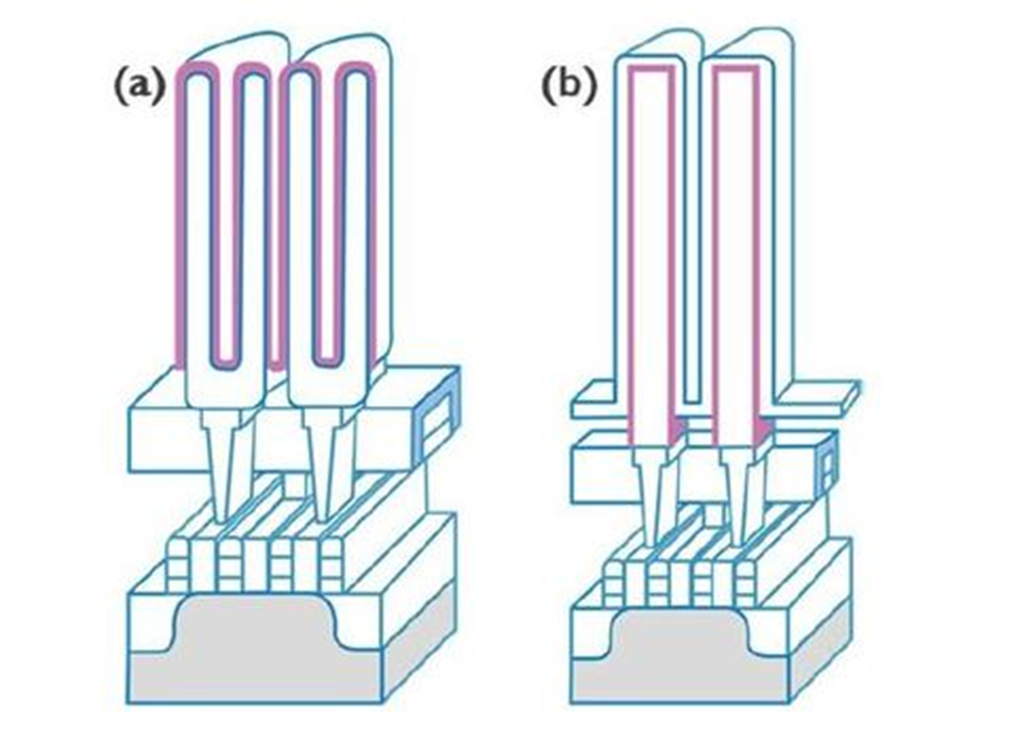

최근 DRAM의 Capacitor는 실린더형에서 기둥형 (pilar)으로 변형되었습니다. 기둥형으로 capacitor를 제조하면 공정이 용이하다는 장점이 있습니다. 하지만 전자의 저장 용량이 저하된다는 단점도 존재합니다. 저장용량이 저하되는데도 pilar형 capacitor를 사용하는 이유는 미세화에 따라 얇고 점점 더 길어지는 capacitor에 쓰러짐이 발생하는 이슈가 존재했기 때문입니다. 그래서 지지대를 1개에서 2개로 늘려서 쓰러짐을 방지하는 double 필러형으로 기술이 진화되었습니다. double pilar 형은 기둥을 한 번에 제작하는 것이 아니라 두 번에 걸쳐 쌓기 때문에 캐패시터를 좀 더 견고하게 만들 수 있어 쓰러짐 이슈를 개선시킬 수 있습니다.

[꼬리 3-1]. Capacitor의 구조로는 현재 정전용량을 키우는데 한계가 있어요. 이를 개선하기 위해서는요?

맞습니다. 현재 DRAM Capacitor의 정전용량을 향상시키기 위해 length와 area의 물리적인 제어를 통해서는 한계에 봉착했습니다. 그래서 도입된 것이 바로 high-k 소재의 도입입니다. 높은 유전율을 가지는 high-k 소재를 도입함으로써 정전용량을 키우는 방법이 채택되었습니다. 대표적인 high-k 소재는 HfO2와 ZrO2입니다. 최근 삼성전자와 SK하이닉스에서 HKMG 공정을 도입하여 메모리 성능을 크게 향상시켰던 것으로 알고 있습니다. HKMG 공정은 소자의 저전력 동작이 가능하며, 누설전류를 최소화시켜 성능과 신뢰성 향상을 극대화시킬 수 있습니다.

'반도체사관학교 훈련과정 > 제품' 카테고리의 다른 글

| [NAND Flash (낸드플래시) #2] "Cell level, SLC MLC, TLC에 대해서 설명하세요" (0) | 2022.03.03 |

|---|---|

| [NAND Flash (낸드플래시) #1] "낸드플래시, 플로팅게이트, NAND / NOR Flash" (9) | 2022.03.03 |

| [DRAM #1] "Dynamic Random Access Memory, D램에 대해서 설명하세요" (14) | 2022.03.02 |

| [DDR & LPDDR] "#DRAM, DDR & LPDDR에 대해서 설명해보세요" (0) | 2022.03.02 |

| [차세대 메모리] "Processing-In-Memory, PIM '차세대 메모리'" (1) | 2022.03.02 |

최근댓글