반응형

여러분들 DRAM의 구조부터 동작원리, 차세대 DRAM 까지 모두 알아보았습니다. DRAM 동작원리가 직관적으로 이해가 안 간다고 많은 분들이 피드백해주셔서, 이번 장을 통해 조금 더 상세하게 다루어보도록 하겠습니다.

★알림★ : 그림에서 Row Address Decoder와 연결된 buffer는 Row Address Buffer입니다ㅠ. 오타

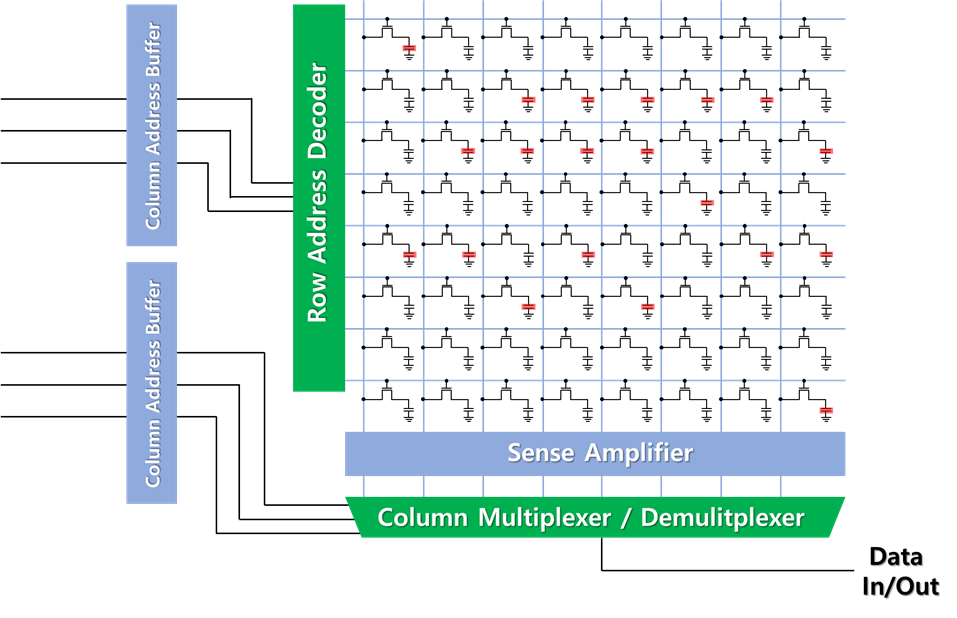

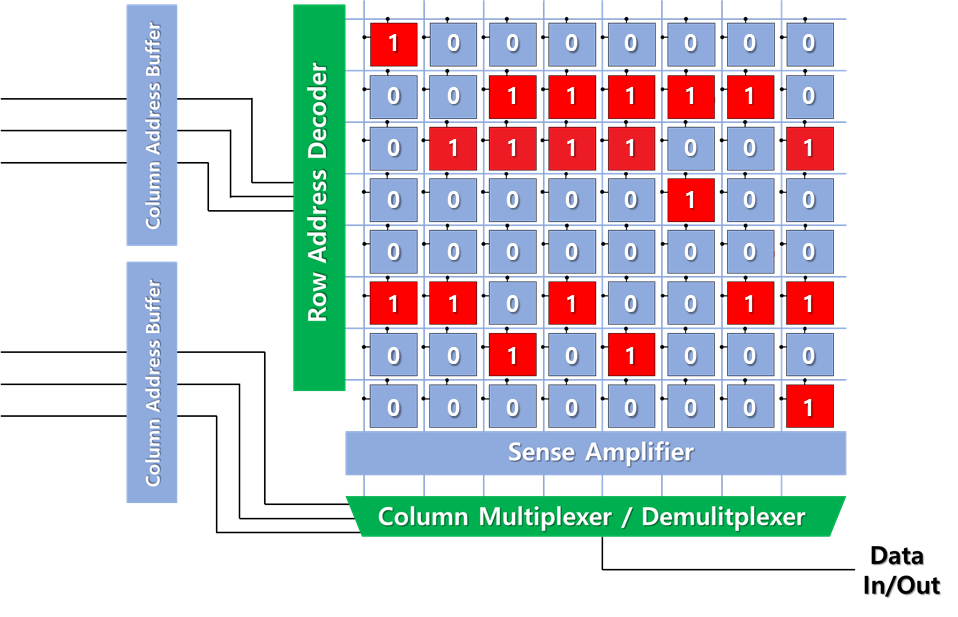

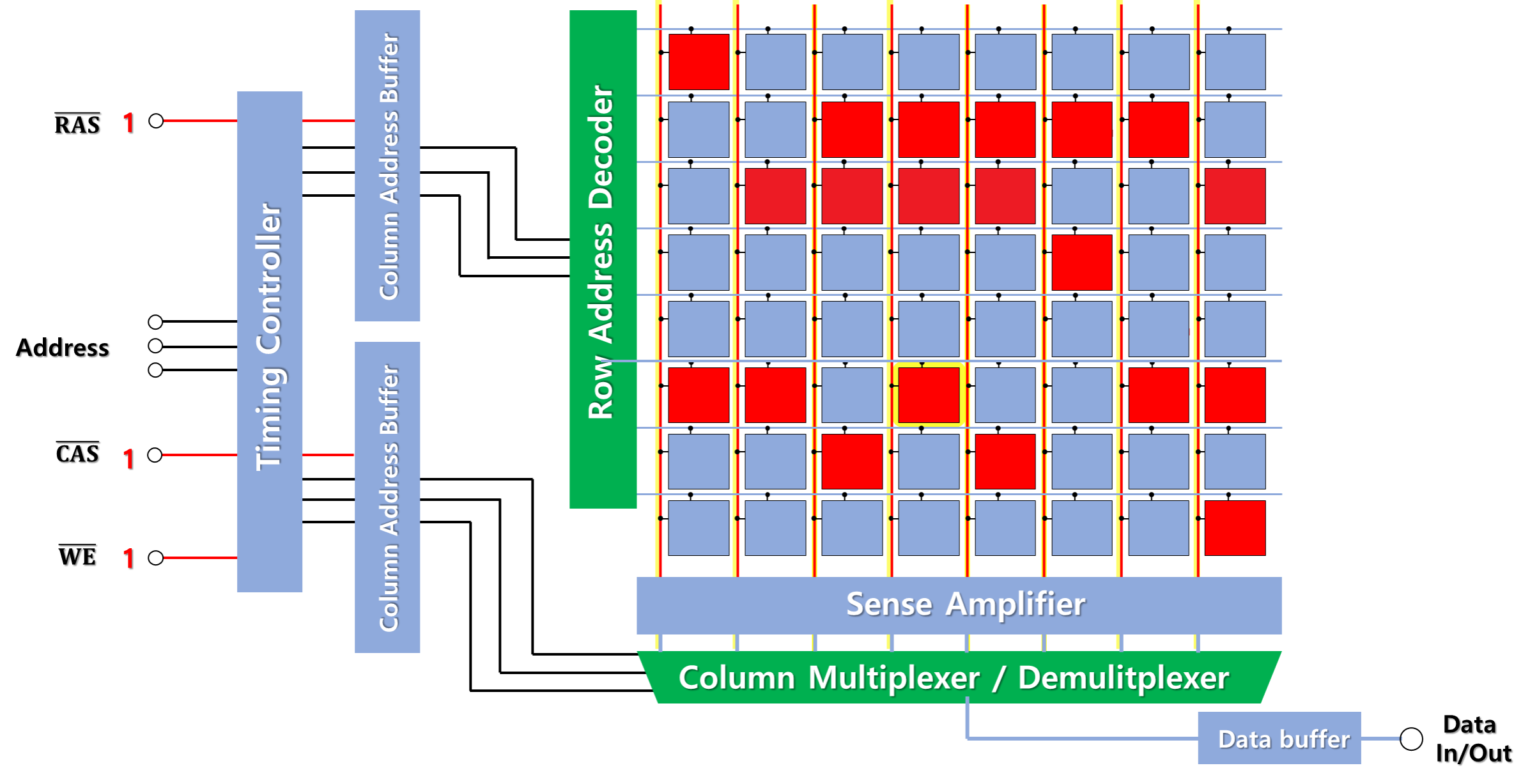

Dynamic Random Access Memory, DRAM은 각 셀이 Transistor와 Capacitor를 포함하는 사각형의 Array로 배열된 수십억개의 셀로 구성됩니다. Capacitor에 전자가 축적되면 '1', 방전되면 셀에 '0'이 기록됩니다. 각 트랜지스터는 수평 Word Line과 수직 Bit Line에 연결됩니다. word line은 transistor의 gate의 on/off를 담당하고, Bit Line은 data를 읽기/쓰기 역할을 수행합니다. 회로를 조금 더 단순하게 보기 위해 8 x 8 행과 열에 대한 메모리 Array를 지원하는 구성요소에 초점을 맞추어보도록 하겠습니다.

위 그림은 8x8 memory array을 보여줍니다. 각각의 구성요소와 DRAM이 어떻게 동작원리를 직관적으로 이해하실 수 있게 다루어보도록 하겠습니다. 위와 같이 Capacitor에 빨간 box가 있는 영역은 전자가 충전되어 셀 내에서는 '1'로 데이터를 인지합니다. 우선 DRAM의 읽고 출력하는 단계를 살펴보겠습니다. 우선 특정 메모리 address를 식별하기 위해 함께 작동하는 구성요소 중 일부를 그림으로 나타내보았습니다.

각각의 셀에 해당하는 메모리 주소가 있으며, 메모리주소를 전달하려면 총 64개의 셀인 8x8 셀 어레이에 대한 Address bus가 필요합니다. 그래서 6개의 line bus가 필요합니다. (2^6=64) 총 64개의 이진 값이 정확히 8x8 Array의 각 셀을 고유하게 실별하는데 필요한 개수입니다. Address bus의 3개 라인은 Row address buffer로 알려진 latch group에 공급되며, 이 latch는 Row Address Decoder에 연결됩니다. 3개의 Address line에 의해 전달되는 이진 값들은 셀 Array 내에서 하나의 특정 행을 고유하게 식별하므로, 이 값은 '행 주소'로 알려져 있습니다.

Address line의 다른 3개 라인은 Column Address buffer로 알려진 latch 그룹에 공급됩니다. 그림과 같이 Column multiplexer & demultiplexer에 연결됩니다. 이 3개의 Address line에 의해 전달되는 이진 값은 Array에서 하나의 특정 column을 고유하게 식별할 수 있습니다. Column과 Row address buffer를 구성하는 래치는 이름에서 알 수 있듯이, 행주소와 열주소 래치를 임시로 저장합니다.

Column & Row address buffer는 메모리 주소 다중화로 알려진 시스템으로 인해 행주소와 열주소를 메모리 모듈에 별도로 입력할 수 있습니다. 다중화 시스템을 사용하지 않으면 수십억개의 메모리 셀을 가지는 메모리 Chip에서 수많은 외부 핀을 가지고 있어야 합니다. 이렇게 외부 핀의 수를 유지하는 것이 더 많은 Memory Address를 가지는 고용량 메모리에서 매우 중요합니다. 6bit memory address는 3개의 외부 pin이면 가능합니다. 32bit memory address는 16개의 adress pins이 요구됩니다. 일반적인 DRAM은 정말 많은 데이터 핀이 존재합니다.

외부 핀은 메모리주소와 데이터 뿐만 아니라 전원 및 다양한 제어 신호를 전달할 때 필요합니다. 예를 들어 각 버퍼에 추가 핀이 RAS, CAS 같은 추가 핀이 필요합니다. 이는 Memory address가 입력되는 동안 RAS는 row address strobe이며, CAS는 column address strobe입니다. 여기서 Stobe의 의미는 DRAM의 접근 시 주소 지정을 위해 사용되는 신호입니다. 대개 DRAM은 전체 Address bus를 두 부분으로 나누어 행주소와 열주소를 따로 받아 들입니다. 컴퓨터 메모리 기술에서 RAS는 관련 행 주소를 알려주기 위해 DRAM에 전달되는 신호입니다. DRAM의 데이터 비트는 행주소와 열주소의 교점에 위치하는 하나의 셀에 저장됩니다. CAS는 열행 주소를 확인하기 위해 전달되는 신호입니다.

[세부설명] RAS, CAS

메모리는 정보를 저장(Write) 혹은 저장된 정보를 읽기(Read) 위해 셀 array의 열과 행으로 구성된 matrix 구조의 주소를 가지고 있습니다. 프로세서가 메모리에 있는 정보를 읽거나 기록할 때, 먼저 행에 신호 RAS를 보내고 나서 열에 CAS 신호를 보내어 Address를 확인합니다. 어떤 memory address에 데이터가 있는지 없는지는 CAS가 담당합니다. CAS 신호가 없어지면 그 Memory 주소에 새로운 정보를 다시 저장합니다.

메모리의 동작과정을 우선 간단하게 설명하도록 하겠습니다.

① CPU가 메인보드 칩셋에 데이터를 요청합니다., 그러면 메인보드 칩셋은 그 데이터가 있는 메모리 주소의 행 주소를 메모리로 전송합니다. 이렇게 하는 데에 각각 1싸이클(Hz)이 걸립니다.

② 행 주소가 메모리의 Row address buffer로 들어오게 되면 Sense Amplifier가 그 행에 들어 있는 모든 cell을 읽어냅니다. 이렇게 행 부분을 읽어내는 일을 일으키는 신호는 RAS라고 부르며, 읽는데 걸리는 시간은 RAS-to-CAS delay(RAS와 CAS 사이의 지연시간)이라고 합니다. 이 과정은 2~3 싸이클이 걸립니다.

③ 행 주소만으로는 필요한 데이터가 어디에 위치하고 있는지 알 수 없습니다. 그래서 이번에는 열 주소를 받습니다. 그러면 CAS 신호가 전달되어 정확한 열을 찾습니다. 이때 걸리는 시간을 CAS latency (CAS 지연시간)이라 합니다. 역시 2~3싸이클이 걸립니다.

④ 전달된 행주소와 열주소로 데이터의 위치를 찾았습니다. 메모리 셀에 있는 내용이 Output buffer (or data buffer)로 전달되고 1싸이클이 걸립니다.

⑤ 마지막으로 메인보드의 칩셋이 출력 버퍼의 내용을 읽고 CPU로 전달합니다. 이때 각각 1싸이클, 2싸이클이 걸립니다.

*CAS latency는 컴퓨터 기억장치의 데이터 처리에 필요한 기억 장치상의 열주소를 알려주기 위해 DRAM에 보내는 신호의 누락시간을 의미하빈다. DRAM에 신호가 전달된 후 데이터가 처리될 때까지 걸리는 시간입니다. 단위는 클럭으로 표시합니다.

읽는 과정에서 Bit line이 DRAM 모듈에 공급되는 전압의 약 절반 1/2Vdd으로 pre-charged 단계가 포함됩니다.

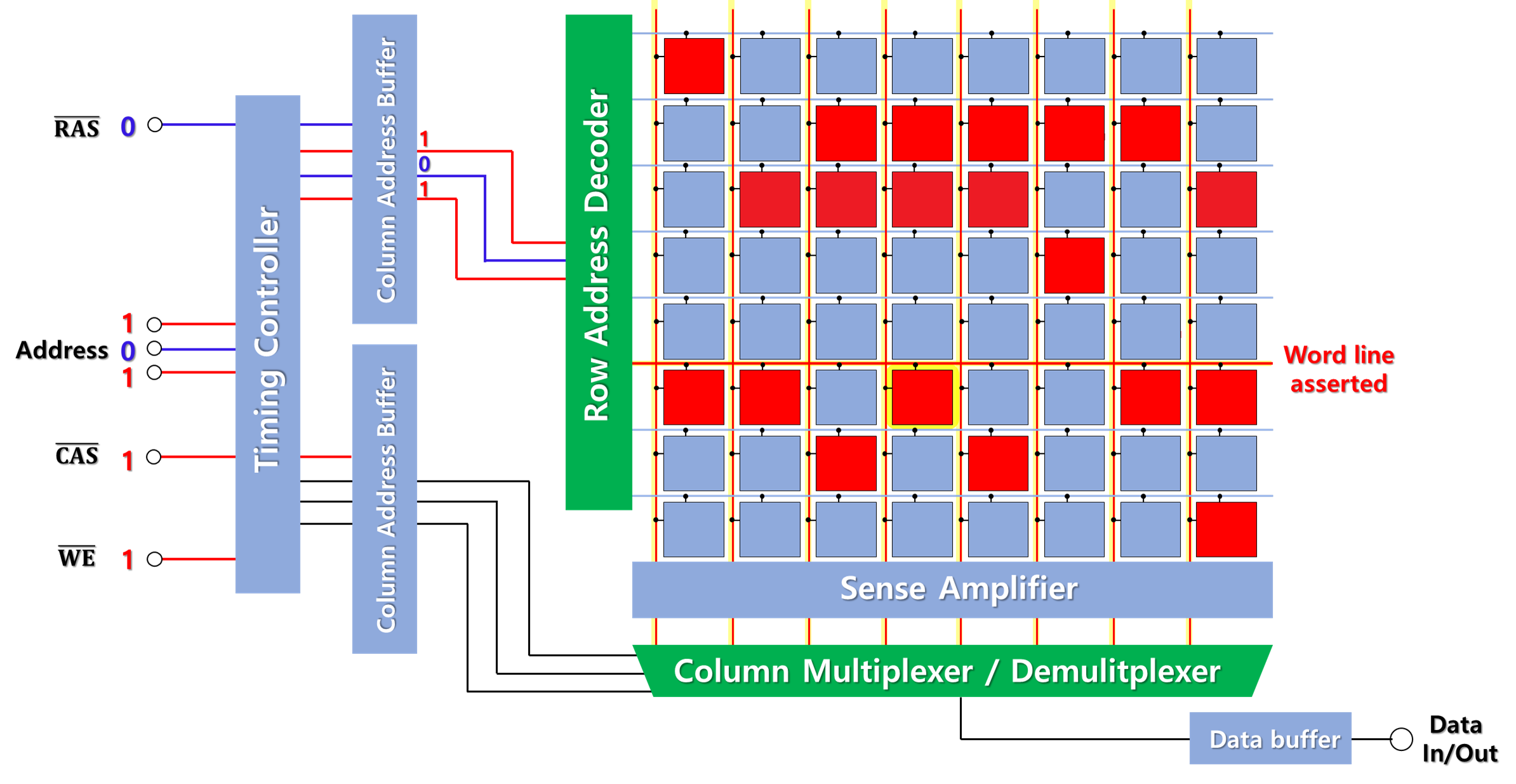

컴퓨터의 Memory controller는 Row address를 pin에 전달하고 RAS는 그와 동시에 활성화 됩니다. Bit line은 pre-charge 회로에서 분리되고 디코딩 된 행주소가 floating 됩니다. 위 그림에서 디코더는 3bit 메모리 주소를 사용하여 8개의 가능한 출력 중 하나만 선택하고, 선택된 word line에 전압이 인가됩니다. 전체 row 행들의 cell values은 sense amplifier에 latch 됩니다. 이때, 우리가 읽고자 하는 cell도 포함하고 있습니다. Cell의 값을 read하는 것은 destructive한 과정으로 원하는 셀을 포함하는 모든 행의 셀들 중, '1'의 값을 가지는 Cell은 부분적으로 discharge되고, '0'인 Cell들은 부분적으로 charing 되는 효과가 있습니다. 그럼에도 불구하고 아래 그림과 같이 셀의 기존 데이터들은 안전하게 sense amplifier에 latch 됩니다. ('latcth'는 나중에 회로에서 다루도록 하겠지만 단지, 1 bit를 저장했다고 생각하면 됩니다.)

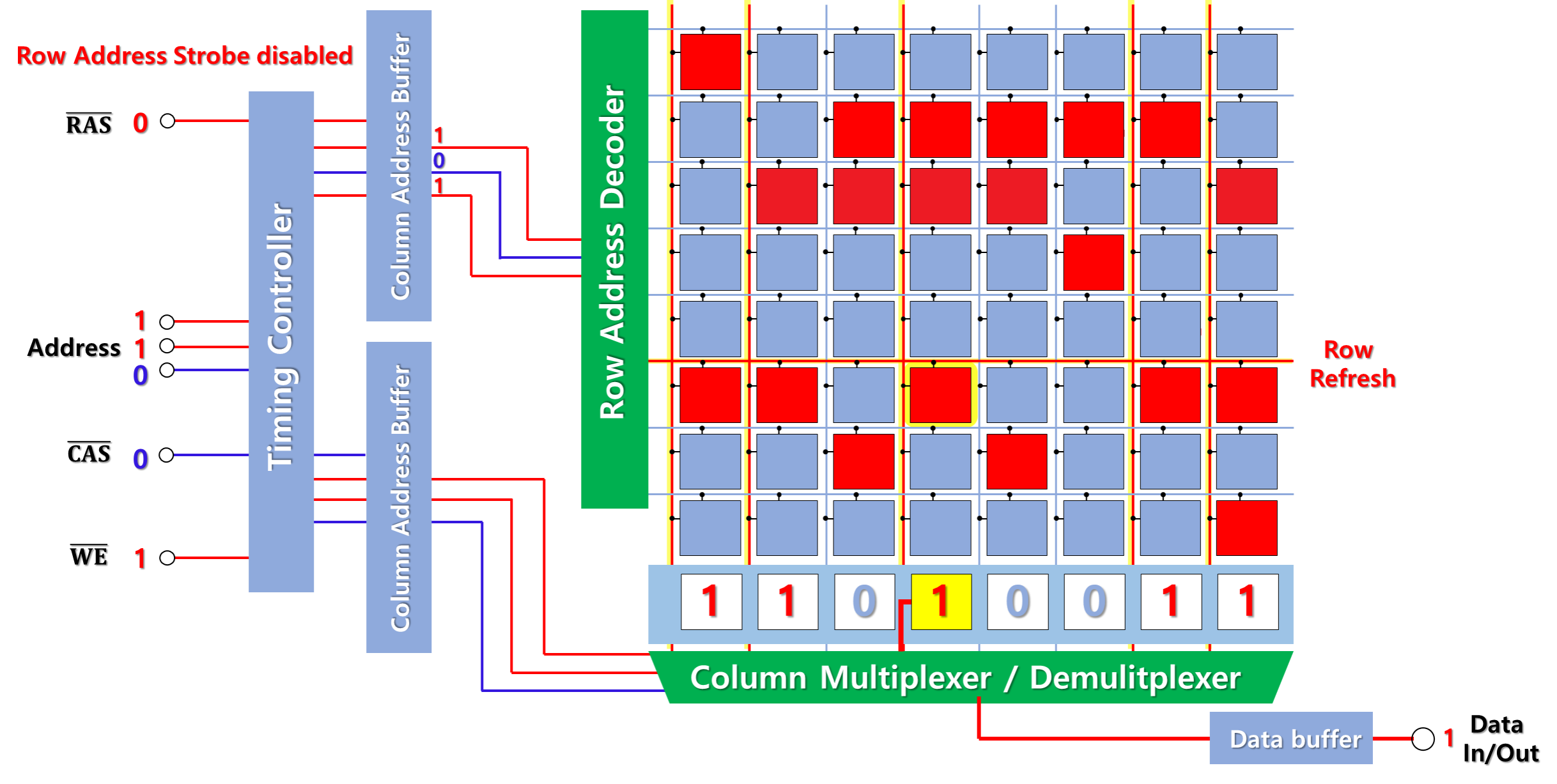

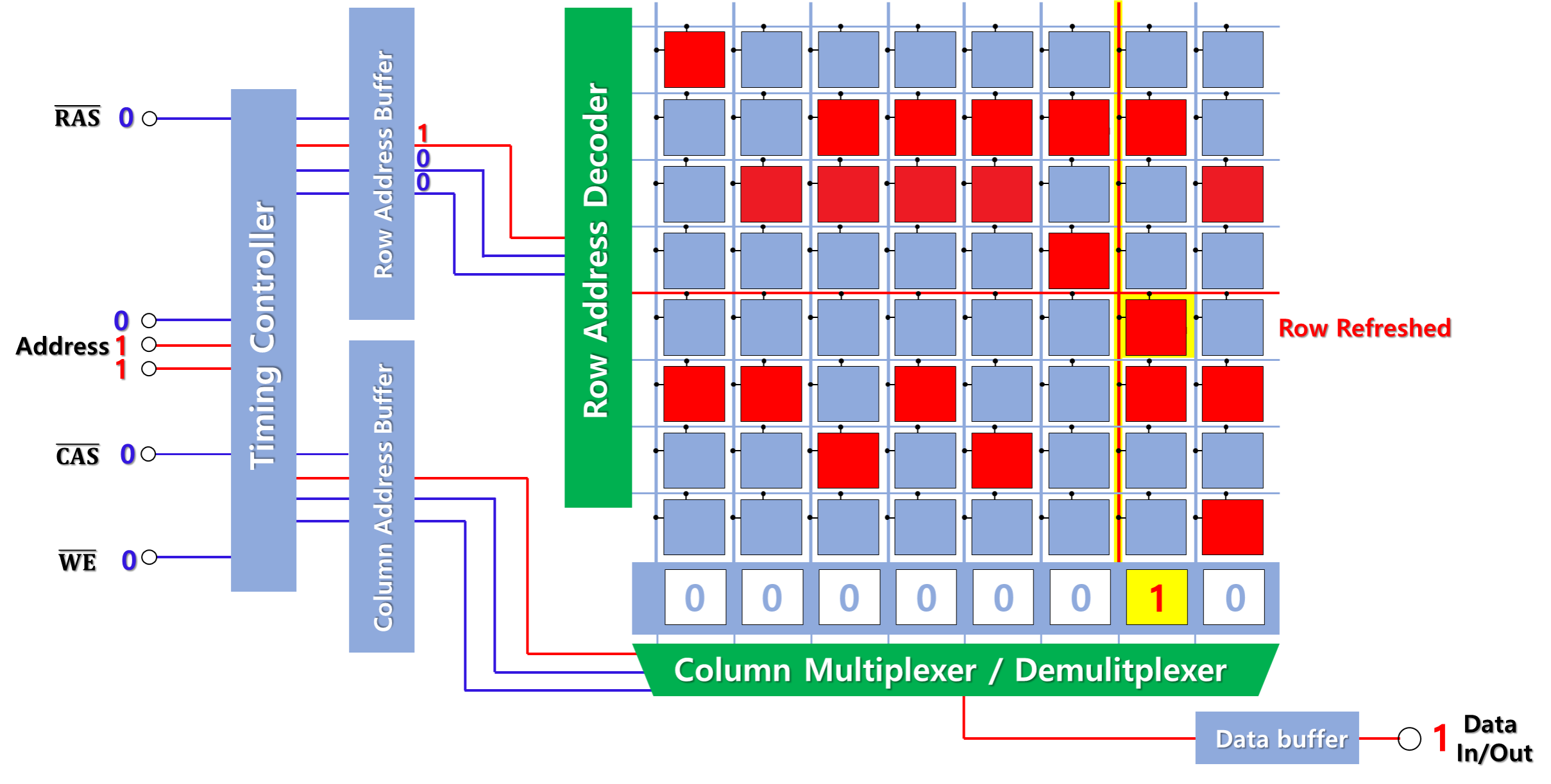

Memory Controller에서 Column address가 Column pin에 입력되면 CAS가 활성화되고, Column address가 Column address buffer에 latch됩니다. Column address는 column multiplexer에서 Sense Amplifier multiplexer 중 하나의 적절한 출력 값을 선택합니다. 아래 그림과 같이 Column multiplexer의 입력 가능한 값은 8개이고 그 중 하나의 출력값을 선택하는 것입니다. 이때의 출력 값이 Data buffer로 이동하여 Cell의 데이터를 출력하게 됩니다.

Row Address Strobe, RAS는 비활성화 되고 출력 외부 데이터 pin이 사용 가능해지면 read cycle 마지막 단계에서 Sense amplifier의 데이터를 사용하여 행을 refresh 작업을 진행합니다. 동시에 Column address strobe, CAS는 비활성화 됩니다.

word line이 desert 되면 출력 data는 더이상 사용할 수가 없습니다. 남은 것은 DRAM의 다음작업 시퀀스에 대비하여 bit line에 pre-charged 시키는 것입니다. 읽기 주기에는 split-second timing이 필요합니다. read cycle에서 일부 다른 작업들이 함께 발생할 수 있기 때문에 다른 작업의 차례를 기다려야 합니다. 궁극적으로 cycle이 빠를수록 좋지만, 정확한 1bit를 가지는 것 또한 매우 중요합니다.

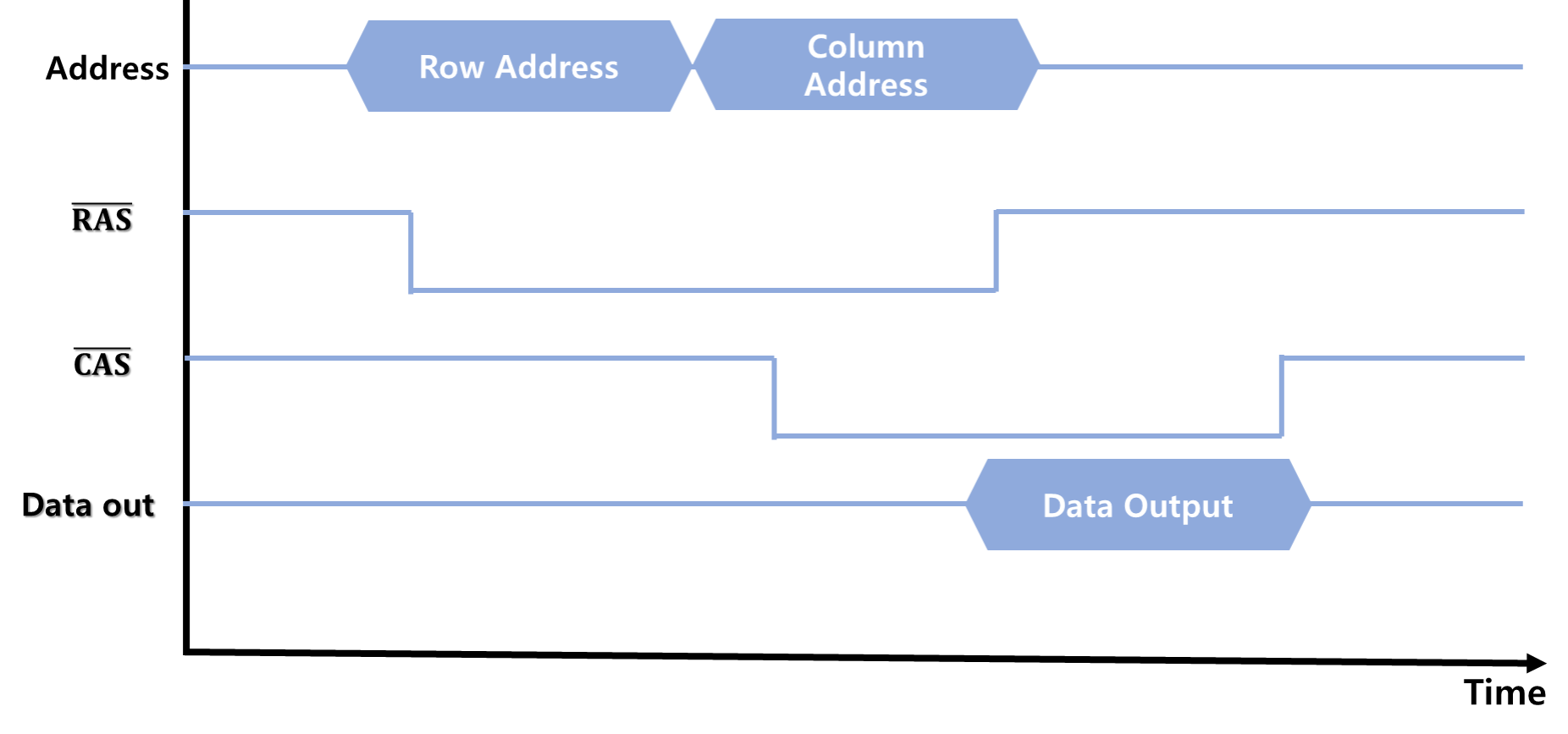

읽기 주기는 위와 같은 다이어그램을고 설명가능합니다. Row address가 외부 adrress pin에 전달됩니다. 신호 전달 지연을 위해 짧은 신호를 허용합니다. 이후 Row Address Strobe, RAS가 활성화 됩니다. 이후 Column address가 외부 pin에서 전달되고 신호지연을 위해 짧은 시간을 허용하면서 CAS가 활성화 됩니다. RAS가 비활성화 되면 data를 출력할 수 있게 됩니다. 이때, Data 출력은 CAS가 비활성화 될 때까지 사용가능합니다. 여기까지가 Read cycle입니다.

Write cycle 또한 유사한 구조를 가집니다. 위와 같이 DRAM 모듈에서 표시된 cell에 데이터를 쓰고자 합니다. 예를 들어 현재 '0'을 나타내는 cell에 '1'을 쓰고 싶다고 가정해봅니다. Bit line은 미리 pre-charged 상태입니다. 적절한 Row address 가 memory controller에 의해 address pin에 전달됩니다.

외부 핀에 인가된 신호는 Controller를 통해 Row Address Buffer로 decoding 되고 읽고자 하는 Cell을 포함하는 Word Line 하나에 전압이 인가됩니다.

그러면 이전 Read cycle과 같이 sense amplifier에서 Row values를 latch 합니다. read cycle과 이 과정까지는 동일하지만 이 단계에서 입력단에 쓰기 가능 신호가 적용됩니다.

쓰기 가능신호가 적용되면 입력단에 '1'이 데이터가 전달되고, Column Address strobe가 활성화 되면서 해당 쓰고자 하는 셀을 탐색합니다. 이렇게 열주소에 따라 Column Demultiplexer에서 Sense Amplifier에 새로운 Value를 loading하는 작업을 수행합니다.

그런 다음에 행은 이전과 같이 refresh되어 Cell에 '1'의 정보를 저장하게 됩니다.

Refresh 이후에 오른쪽 입력단을 활성화 시켰던 입력이 비활성화되고, Row Address Strobe, RAS 그리고 Column Address Strobe, CAS 순으로 비활성화 되면서 Bit Line은 다시 Pre-charged 상태로 돌아갑니다.

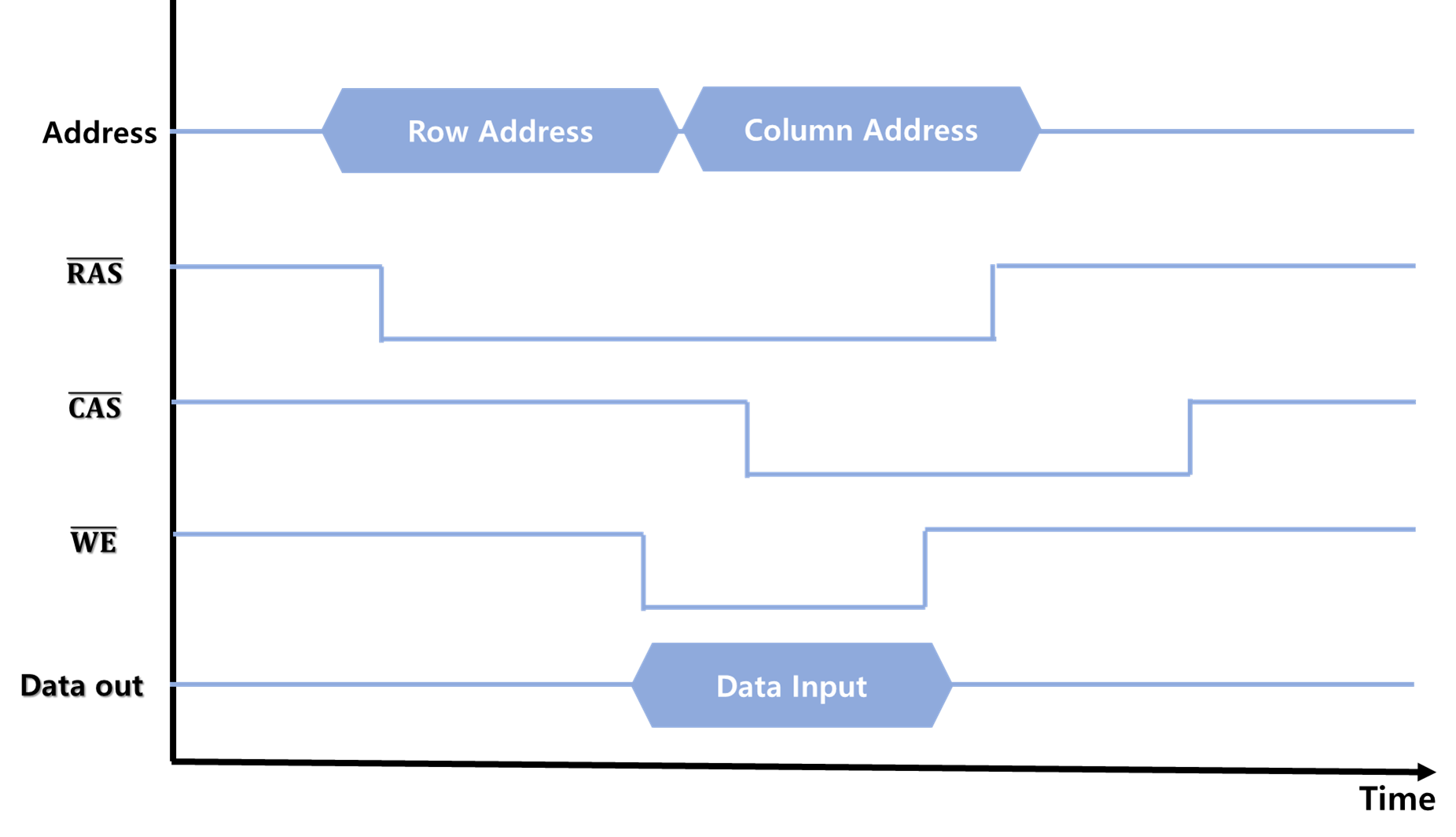

위와 같이 Write cycle의 sequence diagram을 살펴보겠습니다. Row address가 먼저 address pin에 전달되면 역시 신호지연을 고려하여 짧은 시간 오차를 허용하고 RAS가 활성화 됩니다. 이후 Column address도 마찬가지로 address pin에 전달됩니다. WE 신호가 활성화 되면 Input data를 사용할 수가 있고 바로 CAS가 활성화가 됩니다. 그런 다음에 WE가 비활성화 되면 더 이상 Input data는 사용할 수 없으며, 마지막으로 RAS, CAS 순으로 비활성화 됩니다.

하.. 여러분들 제가 회로를 전공한 것이 아니다 보니 표현이 많이 서툰 것 같았습니다. 공부하시면서 피드백 꼭 부탁드리겠습니다.

반응형

그리드형(광고전용)

'반도체사관학교 훈련과정 > 제품' 카테고리의 다른 글

| [전력반도체] Power Device, 파워반도체, 화합물 반도체, Isolation 기술 (7) | 2022.05.10 |

|---|---|

| [메모리반도체] "메모리반도체 용어 총정리" (0) | 2022.03.05 |

| [시스템반도체] "시스템반도체 용어 총정리" (0) | 2022.03.04 |

| [NAND Flash (낸드플래시) #4] "3D NAND, V-NAND에 대해서 설명하세요" (3) | 2022.03.04 |

| [NAND Flash (낸드플래시) #3] "Charge Trap Flash, CTF에 대해서 설명하세요" (1) | 2022.03.04 |

최근댓글