반응형

이전 포스팅에서는 Bulk MOSFET의 6가지 Leakage Current Mechanism을 다루어보았습니다. 오늘은 이를 개선하기 위한 공정에 대해서 설명하도록 하겠습니다!

[질문 1]. Retrograde Body Doping Profile에 대해서 설명하세요.

기존 Bulk MOSFET은 Uniform Body Doping Profile을 채택했습니다. 소자 Dimension이 점점 미세화 되면서 Leakage Current 이슈가 발생했습니다. 그래서 Non-Uniform Body Doping Profile이 채택되었습니다. Retrograde Body Doping Profile은 급경사 Body Doping으로 Doping 기판 깊이에 따라 Doping 농도를 달리하여 기존 Uniform Doping Wdep을 줄이면서 SCE를 효과적으로 줄일 수 있게 됐습니다. Retrograde Body Doping Profile은 Vertical, Lateral 두 가지 Type이 존재합니다.

[꼬리 1.1]. Vertical Retrograde Body Doping Profile (A-Profile)에 대해서 설명하세요.

Bulk MOSFET은 기존에 Well을 우선 형성하고, Surface 쪽에 추가적인 Ion Implant 공정을 진행하여 원하는 Spec에 맞는 Threshold Voltage를 Modulation 합니다. A-profile은 표면의 Doping 농도가 높고 기판 방향으로 갈수록 Doping 농도가 낮아집니다. 상대적으로 Surface 부근에 Doping 농도가 높다보니 Depletion Region은 Body 깊이 방향으로 확장되고 Wdep이 커지면서 Depletion Capacitance가 급격하게 감소합니다. 이는 Body Effect Coefficient, η=Cdep/Cox를 줄임으로써 Body Bias에 따라 Threshold Voltage가 변하는 Body Effect를 최소화 할 수 있습니다.

'Vt(Vsb)=Vt0+ηVsb'. Body Effect를 줄일 수 있는 이점이 있지만, Short Channel Effect에 매우 취약합니다. Surface 부근에 Doping 농도가 높아, Body와 Drain 사이의 Doping 농도 차이가 커지면서 Electric Field가 심화되고 이는 Hot Carrier Injection 현상이 심해 열화현상 및 GIDL Current를 증가시킵니다. 또한 Body 깊이 방향의 낮은 Doping 농도에 의해 Drain Voltage에 의한 Depletion Region이 Body 깊숙이 확장되면서 Channel 아래 Substrate에서 Drain/Source Depletion Region이 맞닿아 급격한 Leakage Current가 발생하는 Punch Through 현상이 증가합니다.

[꼬리 1.2]. Vertical Retrograde Body Doping Profile (B-Profile)에 대해서 설명하세요.

두 번째 Retrograde Body Doping Profile은 Surface 부근에는 상대적으로 낮은 Doping 농도, Body 깊이 방향으로 Doping 농도를 증가시킵니다. 이는 표면에 낮은 Doping 농도로 인해 Electric Field가 완화되어 Hot Carrier Injection을 억제합니다. 또한 Dopant 농도가 낮아, Impurity Scattering이 감소하여 Carrier Mobility가 증가하여, Velocity Saturation을 억제합니다. 또한 Body 깊이 방향에 상대적으로 높은 Doping 농도로 인해 Drain Voltage에 의한 Depletion Region이 확장되는 것을 억제되면서 Punch Through 현상을 방지합니다. 하지만 Body 깊이 방향의 Doping 농도가 높아 Gate Voltage 인가 시 Channel 아래 Depletion Region이 확장되는 Wdmax가 Uniform Doping Profile보다도 작습니다. 이는 Cdep이 일정 수준의 값을 가지게 되고, 상대적으로 높은 Body Effect Coefficient를 가지게 됩니다. 따라서 Vt(Vsb)=Vt0+ηVsb, (η=Cdep/Cox)' Body Effect가 커지면서 회로 상에 Body 단자에 Bias에 의해 원하지 않는 Threshold Voltage의 변화가 일어날 수 있습니다.

[꼬리 1.3]. Velocity Saturation에 대해서 설명하세요.

MOSFET의 Channel Thickness는 수나노로 매우 좁습니다. 이는 즉, Channel Resistance가 높다는 것을 의미합니다. Oxide Thickness가 점점 얇아지면서 Gate Voltage에 의한 Vertical Electric Field에 의해 Carrier가 좁은 Channel 영역에서 충돌하면서 Drain 방향으로 Drift 됩니다. 충돌 횟수가 많아지면서 Mean Free Path, MFP가 짧아지고 Carrier Mobility가 작아집니다. Vertical Retrograde Body Doping A-Profile의 경우, 표면에 높은 Doping 농도 때문에 Impurity Scattering이 심하고 이는 Carrier Mobility를 더욱 심하게 저하시킵니다. 그로 인해 Channel Length가 짧아지면서 소자의 On-state Current가 높아지길 기대했지만, Carrier Mobility 저하되면서 Carrier Velocity가 더욱 빠르게 Saturation 됩니다. Carrier Velocity와 Electric Field의 관계는 Id-Vds의 관계와 일맥상통합니다. Carrier Mobility의 감소로 Velocity Saturation이 발생하고, Short Channel Device에서 더 낮은 On-state Current가 흐르면서 소자 Performance가 심각하게 저하됩니다.

[질문 2]. Lateral Retrograde Body Doping Profile에 대해서 설명하세요.

이번 Lateral Retrograde Body Doping Profile은 우리가 많이 알고 있는 Lightly Doped Drain, LDD와 Halo Doping (or Pocket Implant)가 있습니다. Lateral Retrograde Body Doping Profile은 Doping 농도를 조절함으로써 기존 Bulk MOSFET에서 발생하는 SCE를 효율적으로 억제할 수 있습니다. 하지만 공정노드가 점점 미세해지면서 이러한 Doping 농도는 Active Domain이 점점 작아지고 공정이 어려워지고 있어 새로운 구조의 소자에 적용하기 위해 많은 연구가 이루어지고 있습니다.

[꼬리 2.1]. Lightly Doped Drain, LDD 공정에 대해서 설명하세요.

SCE를 억제하기 위해서는 표면의 Electric Field를 완화시켜야 합니다. 그러기 위해서 Body Doping 농도 Na를 낮춘다면, Threshold Voltage가 증가하게 되면서 소자 Performance를 저하시킵니다. 그렇다면 Body Doping이 아닌, Drain 농도를 Engineering 합니다. 만일 Drain Doping 농도를 낮춘다면, Source/Drain Output Resistance가 증가하면서 이 역시 소자 Performance 저하와 직결됩니다. 그래서 Channel과 맞닿는 Source/Drain의 n+ 영역에 n- Doping을 해주는 기법이 채택되었습니다. 이는 Surface 부근의 Electric Field를 완화시켜 Hot Carrier Injection을 억제할 수 있으며, 비교적 Process가 간단합니다.

[꼬리 2.2]. Shallow Junction Depth Profile에 대해서 설명하세요.

Source/Drain의 Junction Depth, Xj를 얇게 함으로써 Channel 부근의 Depletion Region을 감소시킬 수 있습니다. 이는 Electric Field를 효과적으로 완화시킬 수 있으며, Hot Carrier Injection과 Source 방향으로 확장되는 Depletion Region을 억제함으로써 DIBL Effect를 완화시킬 수 있습니다. 뿐만 아니라, Junction Depth가 얇아지면서 Junction Edge에 집중되는 Electric Field를 완화시켜 Body 깊이 방향으로 확장되는 Depletion Region을 억제해 Punch Through 현상 또한 방지할 수 있습니다. 그리고 Junction Capacitance가 감소하게 되면서 Parasitic Capacitance를 효과적으로 감소시켜, Body Factor 또한 줄이면서 Subthreshold Swing 특성을 향상시킬 수 있습니다.

[꼬리 2.3]. Halo Doping (or Pocket Implant)에 대해서 설명하세요.

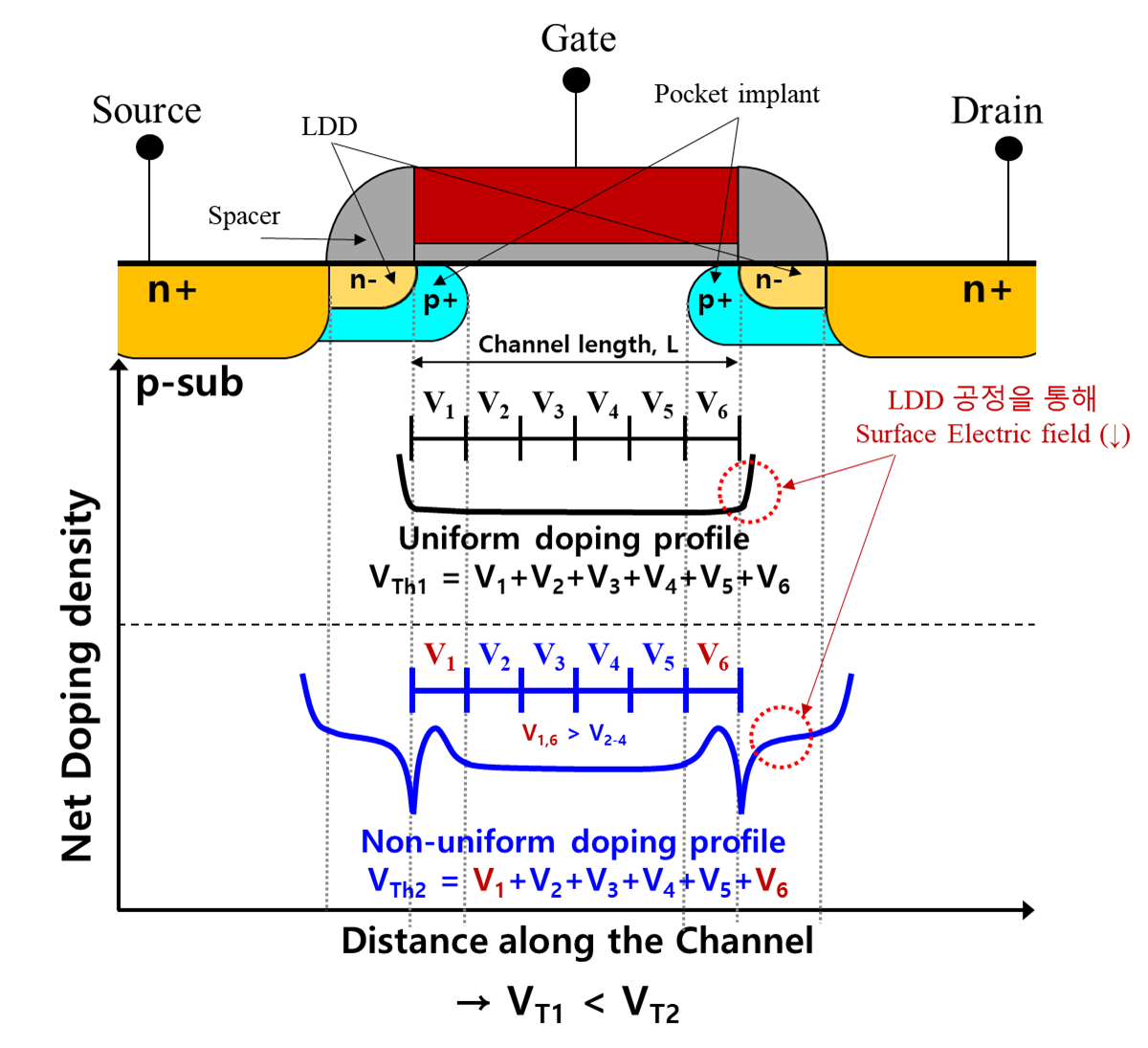

Halo Doping (or Pocket Implant)는 Source / Drain와 Substrate 간 Contact 영역을 High p+ Doping을 해주는 기법입니다. Junction Edge에서 Substrate 방향으로 Depletion Region 확장을 억제하면서 Punch Through 현상을 방지할 수 있습니다. High p+ Doping에 의해 Potential Barrier를 상승시키면서 p+ Doping 영역에 Channel Thickness가 감소하게 됩니다. 그로 인해 Carrier가 Channel에 갇히게 되고 Channel에 Carrier Concentration이 증가하여 Vt를 상승시킵니다. 이를 좀 더 간단하게 설명드리자면, 전체 채널 영역을 아래와 같이 여러 구간으로 나눕니다. Na Doping 농도가 높으면 Vt가 증가하는 것은 알고 계실 것입니다. Uniform Body Doping의 경우 V1~V6 모두 같은 전위 값을 가지지만, Halo p+ Doping이 적용된 소자의 경우 V1=V6 > V2-V4 이기 때문에 전체 평균 Vt가 기존 Uniform Doping Profile보다 향상되는 것을 알 수 있습니다. 그리고 아래와 같이 LDD 공정이 적용되면 Drain과 Body가 맞닿는 부분의 Doping 농도 차이를 줄여줌으로써 Electric Field가 완화되면서 SCE를 억제할 수 있습니다.

[질문 3]. Subthreshold Swing, St를 향상시키는 방법에 대해서 설명하세요.

Subthreshold Swing은 log(Id)-Vgs의 Slope의 역수입니다. 소자 성능을 향상시키기 위해서는 Threshold Voltage는 작게, On-state Current는 높게, Off-state Current는 낮게 함으로써 Super Steep Slope를 구현해야 합니다. 그러려면 St 값을 낮추어야 합니다. St 값을 낮추기 위해서는 Parasitic Capacitance 값을 낮추어야 합니다. 그러기 위해서는 앞서 말씀드린 방법대로 Shallow Junction Depth를 얇게 해야 합니다. 그리고 Oxide Capacitance, Cox를 높여야 합니다. 그러기 위해서 Oxide Thickness를 얇게하고, 높은 유전율의 High-k 소재가 도입된 것입니다. St=2.3kT/q(1+η)=60mV(1+η), η=Cdep/Cox. 하지만 아무리 이상적인 소자라고 하더라도 Field Effect로 동작하는 FET 소자는 St 값을 60mV/decade 이하로 낮출 수 없습니다. 그것은 Source에서 Channel로 Carrier가 Diffusion Mechanism에 의해 Injection 되기 때문입니다.

MOS Capacitor는 Inversion Layer를 형성하기 위해 Gate Voltage가 인가되면 Body에서 Generation에 의해 Carrier가 Surface 쪽으로 이동하여 Channel을 형성합니다. 하지만 우리가 알고 있는 C-V 곡선을 보시면 High Frequency에서는 동작하지 않는 것을 보셨던 기억이 있을 것입니다. 즉, MOS Capacitor는 고속 Switching 동작이 불가능한 것입니다. (kHz 수준) 그래서 고농도로 Doping된 Source/Drain 단자를 추가하여 Source에서 직접적으로 Channel에 Carrier를 Injection 함으로써 GHz의 고속 Switching이 가능하게 되었습니다. 하지만 집적도가 높아지고 인공지능 AI 연산 분야에서는 이보다 더욱 고속의 소자 성능이 요구됩니다. 하지만 Field Effect 소자는 Source에서 Diffusion Mechanism에 의해 Carrier가 주입되므로 60mV/decade 이하의 값을 가지기 어렵습니다.

이를 개선시키기 위해 Diffusion Mechanism이 아닌 새로운 Mechanism의 FET 소자가 연구되고 있습니다. Pinch-off Region의 Impact Ionization Mechanism을 적용한 I-FET (~5mV/Decade), Source 쪽에 Tunneling Mechanism을 적용한 TFET, 그리고 Ferroelectric 특성의 HfZrO 소재를 사용한 Negative Capacitance, NC-FET이 활발히 연구가 되고 있습니다. NC-FET은 Body Factor, m=1+Cdep/Cox에서 Negative Capacitance 특성을 활용하여 Body Factor를 낮추어 St 값을 ~30mV/decade 까지 낮춘 연구가 있습니다.

[질문 4]. Silicon on Insulator, SOI 기술에 대해서 설명하세요.

Silicon on Insulator, SOI 기술은 현재 반도체 미세공정에서 빠질 수 없는 핵심 기술입니다. Leakage Current의 Main Path는 Source-Body-Drain 경로입니다. 한 연구에서 Body Thickness를 7nm에서 3nm로 줄였을 때, Off-state Current가 1,000배 이상 감소시킨 연구 결과가 있습니다. 이는 Ultra Thin Body, UTB SOI MOSFET 기술입니다. Drain Engineering을 보면 Doping Effect을 적용하면 Carrier Mobility가 감소하거나, LDD, Pocket Implant 공정은 공정 미세화가 가속되면서 공정 복잡도가 증가합니다. SOI 기술은 소자 Structure가 비교적 간단합니다. 간단하게 원리를 살펴보면, 우리는 Off-state Current를 줄이기 위해서는 Depletion Capacitance, Cdep을 감소시켜야 합니다. MOSFET Structure를 보면 Depletion Capacitance와 Oxide Capacitance의 직렬구조로 전압분배법칙에 의해 Gate 구동력 저하로 Off-state Current가 증가한다고 했습니다. 이때, Body 아래를 Insulator로 만들면, Depletion Capacitance와 Body 단자 GND가 없어지면서 Cdep을 제거할 수 있습니다.

[질문 4.1]. Silicon on Insulator, SOI의 이슈에 대해서 설명하세요.

물론 SOI 기술 또한 Issue가 존재합니다. Body Terminal을 Insulator로 교체하면서 Body 내 전하들은 Floating 됩니다. SOI는 보통 Partially Depleted, PD-SOI와 Fully Depleted, FD-SOI로 구분됩니다. PD-SOI는 Body 내에 Neutral Si (Body) 영역이 일부 존재하면서 Floating Body Effect에 의해 동작 간 Vt를 낮추어 전류가 증가하는 Current Kink Effect가 발생합니다. 조금 더 물리적으로 접근하자면, 기존의 MOSFET에서 열적으로 생성된 EHP에서 Electron은 Drain으로 Hole은 Substrate로 빠져나갔습니다. 하지만 Substrate 단자가 없어지면서 Hole은 Body 영역에서 Floating 되고 Source 방향 Well에 축적되면서 Charge Space가 형성됩니다. Positive Charge 영역이 생기면서 소자 동작 간에 Threshold Voltage가 감소하게 됩니다. 그로 인해 Saturation Current가 갑자기 증가하는 Current Kink Effect가 발생하는 것입니다. Fully-Depleted SOI는 Neutral Si Body 영역을 완전히 제거되어 Floating Body Effect를 억제하면서 Current Kink Effect를 방지할 수 있습니다. Fully Depletion이 되기 위해서는 Body Thickness는 더욱 얇아져야 하며, Buried Oxide 두께는 두꺼워야 합니다.

반응형

그리드형(광고전용)

'반도체사관학교 훈련과정 > 반도체 소자' 카테고리의 다른 글

| [반도체 소자] Dynamic/Static Power Current, VCC & VDD 차이 (2) | 2022.06.09 |

|---|---|

| [반도체 소자] Dynamic/Static Power, Vcc, Vdd, Vee, Vss에 대해서 설명하세요. (3) | 2022.04.01 |

| [반도체 소자] 이것만 보면 된다! Leakage Current 총정리 [1/2] (21) | 2022.03.24 |

| [반도체 소자] 3nm/2nm 공정 GAAFET, 반도체 산업 (0) | 2022.02.08 |

| [반도체 소자] 3D MOSFET의 진화, Gate-All-Around / 차세대 소자 (1) | 2022.02.08 |

최근댓글