반응형

안녕하세요.

딴사관 여러분들 금일 다룰 컨텐츠는 공정 정합성 향상을 위해 고려해야 할

Layout Effect 입니다.

질문 1. 공정 정합성 향상을 위한 Layout Dependant Effect (LDE)에 대해서 알고 있나요.

공정에서 Silicon 값과 SPICE Model 간의 Mismatch를 개선하기 위해서는 Layout Effect을 고려해야 하는 것은 매우 중요합니다. 특히 Layout Effect의 경우, 동일 Device라 하더라도 Narrow/Short Device와 같이 Small Device일수록 Variation의 더욱 취약합니다. 따라서, 공정 정합성을 향상시키기 위해서 Layout Effect이 미치는 영향에 대해한 Factor를 꼭 반영하여 회로 성능을 예측하고 설계해야 합니다. 대표적인 Layout Effect으로는 Well Proximity Effect (WPE), Shallow Trench Isolation (STI) Stress Effect, Pattern Density Effect 등이 있습니다.

질문 2. Well Proximity Effect (WPE)에 대해서 설명해주세요.

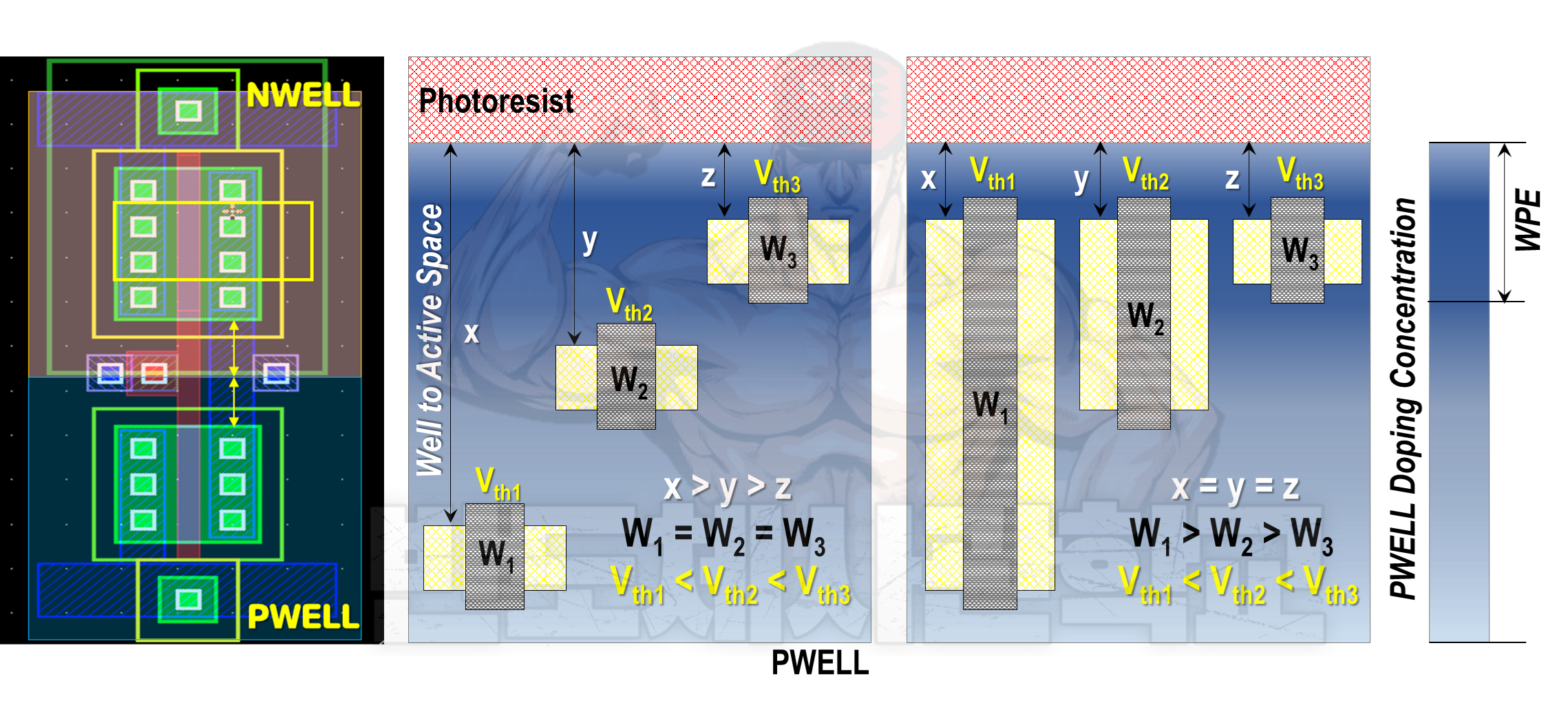

Well Proximity Effect (WPE)는 Device가 Well Edge에 가까이 위치할 때, Vth가 상향하는 현상입니다. WPE는 이온주입 시 Photoresist의 Sidewall에서 Ion Scatttering에 의해 Well Edge 부근의 Doping 농도가 상대적으로 높아지게 됩니다. 그로 인해, Well Edge 부근의 Tr.에서 소자 Speed의 차이가 발생하며, 실제 Vth 변화로 Carrier Mobility 및 Body Effet에도 영향을 미칩니다. WPE에 의해서 소자 Vth는 약 ~100mV의 Variation이 발생하게 되면서 공정 정합성을 저하시키는 주 요인이 되겠습니다.

꼬리 2.1. Well Proximity Effect (WPE)를 개선시키기 위해서 어떻게 해야 할까요.

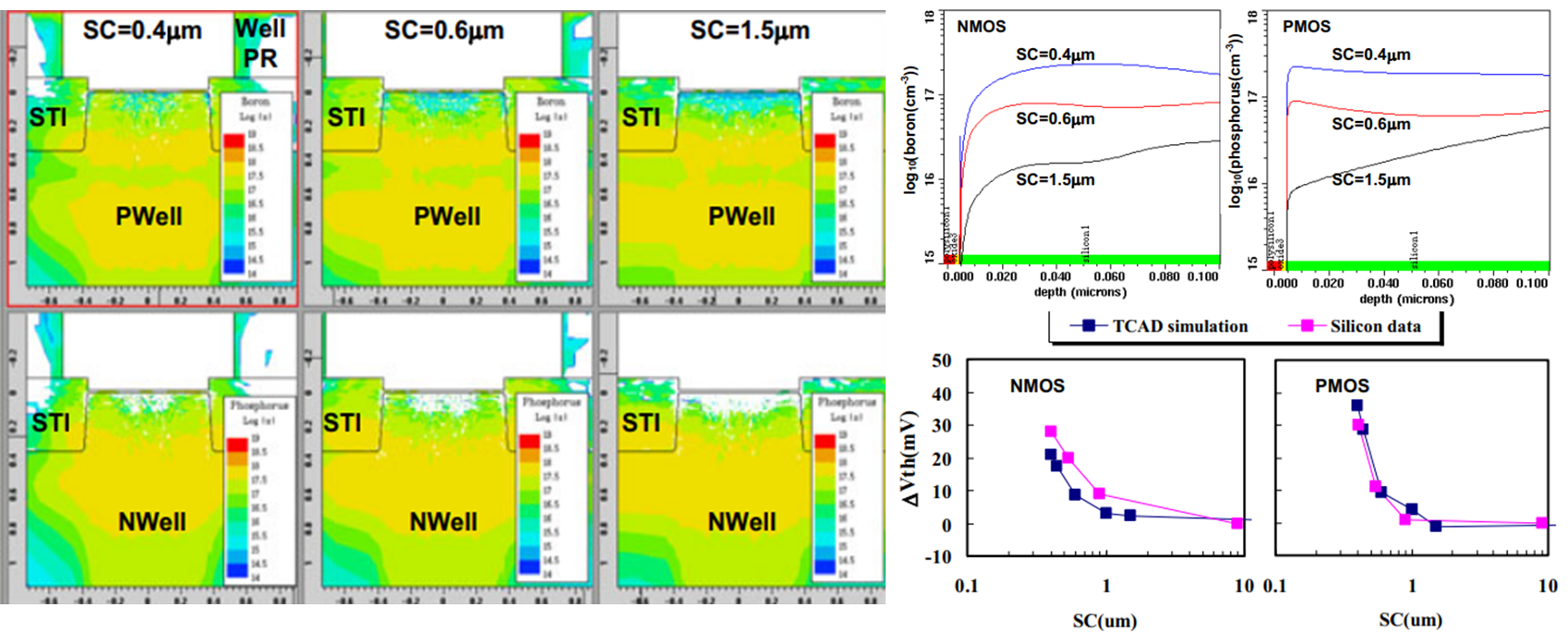

Well Proximity Effect (WPE)는 Well Imp. 이전 노광공정의 PR에 많은 영향을 받습니다. PR의 두께가 두꺼울수록, PR Profile의 Tapered Angle이 작을수록 (사다리꼴 Profile) Ion의 Scattering으로 인한 불균일한 Doping Profile을 갖게 되어 Vth Variation이 심화됩니다.

WPE를 개선시키기 위해서는 공정 Set-up 초기 Well to Active Space를 Split 하여, 조건 별 Vth Variation을 평가하여 WPE의 제약에서 자유로운 Design Rule을 정립해야 합니다. 그리고 Small Device의 영향을 받기에 Tr.의 Active Size를 최적화 하여 WPE 영향을 받지 않는 조건 범위 내에서 Tr. Active Size를 제한해야 합니다.

충분한 Well to Active Space를 확보하지 못할 경우, 불균일한 Well Doping Profile에 기인한 기생 Cap. 발생, Carrier Mobility 저하, Junction BV 하향, 심할 경우 Latch-up과 같은 신뢰성의 열화로 이어질 수 있습니다.

- Well to Active Space가 충분히 확보되었는지, Split 조건 별 △Vth Variation을 평가하여 Design Rule 확립.

- Tr. W/L 별 Size Split 평가를 통해, Size 조건 별 △Vth Variation 평가하여 Tr. Active Size 제한함.

- Well to Active Space (SC)가 가까울수록 WPE에 의해 Well Edge 부근에서 Boron/Phosphorus의 Doping Concentration이 높음. 그로 인해, N/PMOS의 Vth가 증가함.

꼬리 2.2. Photoresist의 두께가 두꺼우면 이런 Layout Effect이 심화된다고 말씀하시는 것일까요.

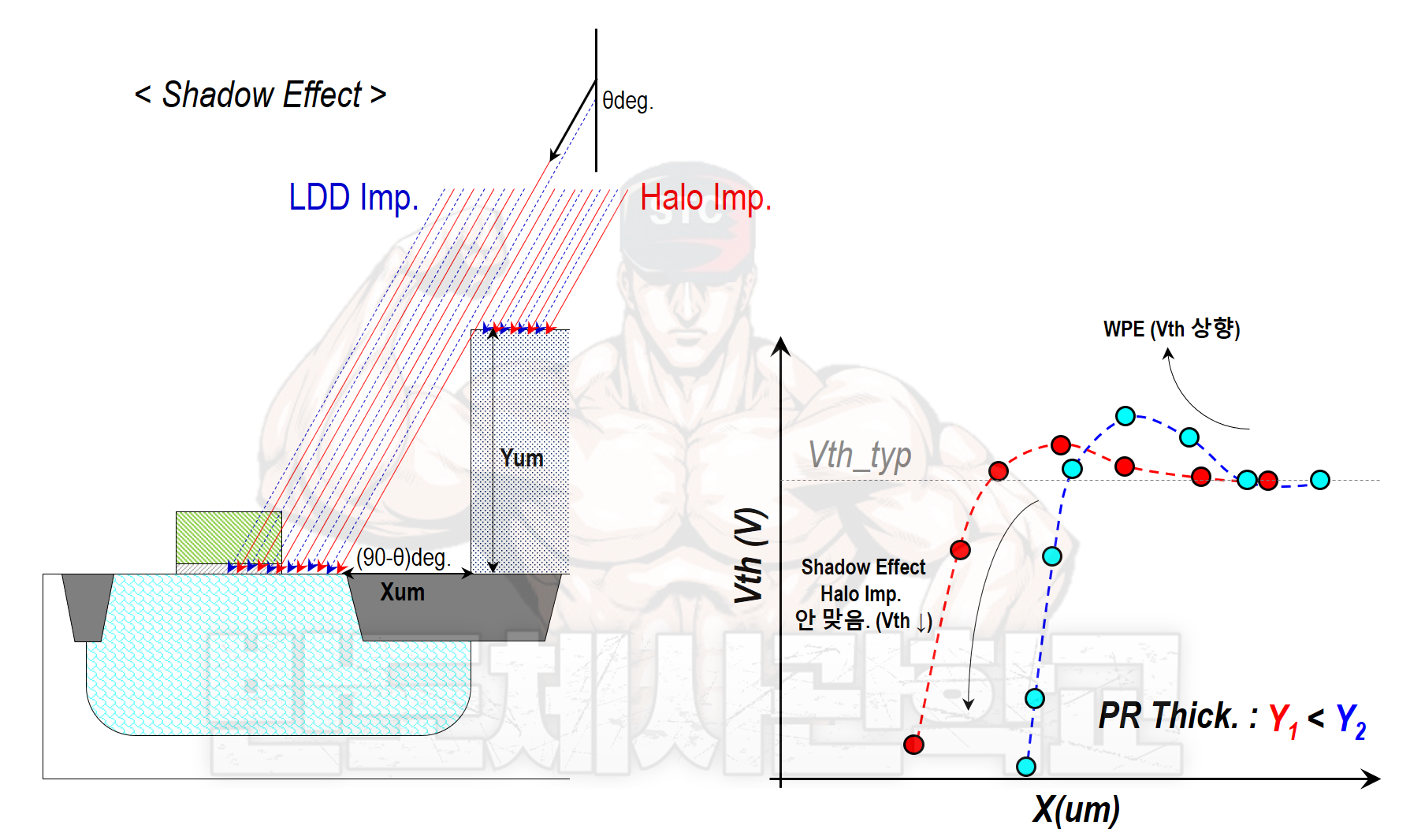

그렇습니다. PR Thickness는 점점 더 node scaling down이 될수록 얇아지고 있습니다. 그 이유는 WPE와 같은 Layout Effect 뿐만 아니라 바로 Shadow Effect 때문이라고 할 수 있습니다. 이온주입 공정 시, 균일한 Doping Profile 혹은 Rp점과 같은 Module Spec.을 Targeting 하기 위해 Tilt를 주어 이온을 Wafer에 입사시킵니다. 이때, PR의 Thickness가 두껍게 되면 Tilt 되어 입사된 이온이 PR에 Blocking이 되면서 원하는 영역에 Doping을 할 수 없게 됩니다.

따라서, PR Thickness를 두껍게 가져가져가야 한다면 WPE 상향 및 Shadow Effect와 같은 Side Effect을 최소화 하기 위해서 충분한 Well to Active Space (X)를 확보해야 합니다.

- 일반적으로 LDD와 Halo Imp.의 경우 Tilt를 주어 Active에 주입됩니다.

- 두꺼운 PR Profile에 충분한 Well to Active Space를 확보하지 않는다면, Vth roll-up 효과를 주는 Halo Imp.가 적용되지 않아 Vth Lowering이 심화되어, 더 이상 소자로서 Function을 상실하게 됩니다.

꼬리 2.3. 그러면 Photoresist의 Thickness를 얇게 가져가면 되겠네요.

앞서 설명드렸다시피 PR의 Thickness와 Profile이 Layout Effect에 큰 영향을 미친다고 말씀드렸습니다. PR의 두께를 얇게 가져가면 WPE와 Shadow Effect에서 상대적으로 자유롭기 때문에 Well to Active Space를 보다 Shrink할 수 있어, 더 미세한 소자를 만들어 낼 수 있습니다. 하지만, 무작정 PR의 Thickness를 얇게 가져갈 수는 없습니다. 그 이유는 PR의 Thickness가 얇아질수록 미세화에는 유리할 수 있으나, Etch Resistance나 Blocking Area에 의도치 않은 Doping이 되어 원하지 않은 Doping Profile을 형성할 수 있기 때문입니다. 그로 인해 미세 node에서는 단일 유기 Resist를 사용하기 보다는 Nitride/Pad Oxide와 같은 무기물로 구성된 Hardmask를 사용하여 공정을 진행합니다.

물론 무기 Hardmask를 사용할 경우, 소자를 미세하게 만들 수 있기 때문에 Chip Size를 Shrink하고, 보다 많은 Net die를 확보할 수 있다는 장점이 있습니다. 반면에 공정 Step이 추가되어 제조비용 또한 상승됩니다. 따라서, Application 관점, 공정 및 DIE Cost 측면 등 면밀한 사업성 검토를 통해 선택해야 할 사항입니다.

질문 3. Shallow Trench Isolation (STI) Stress Effect에 대해서 설명해주세요.

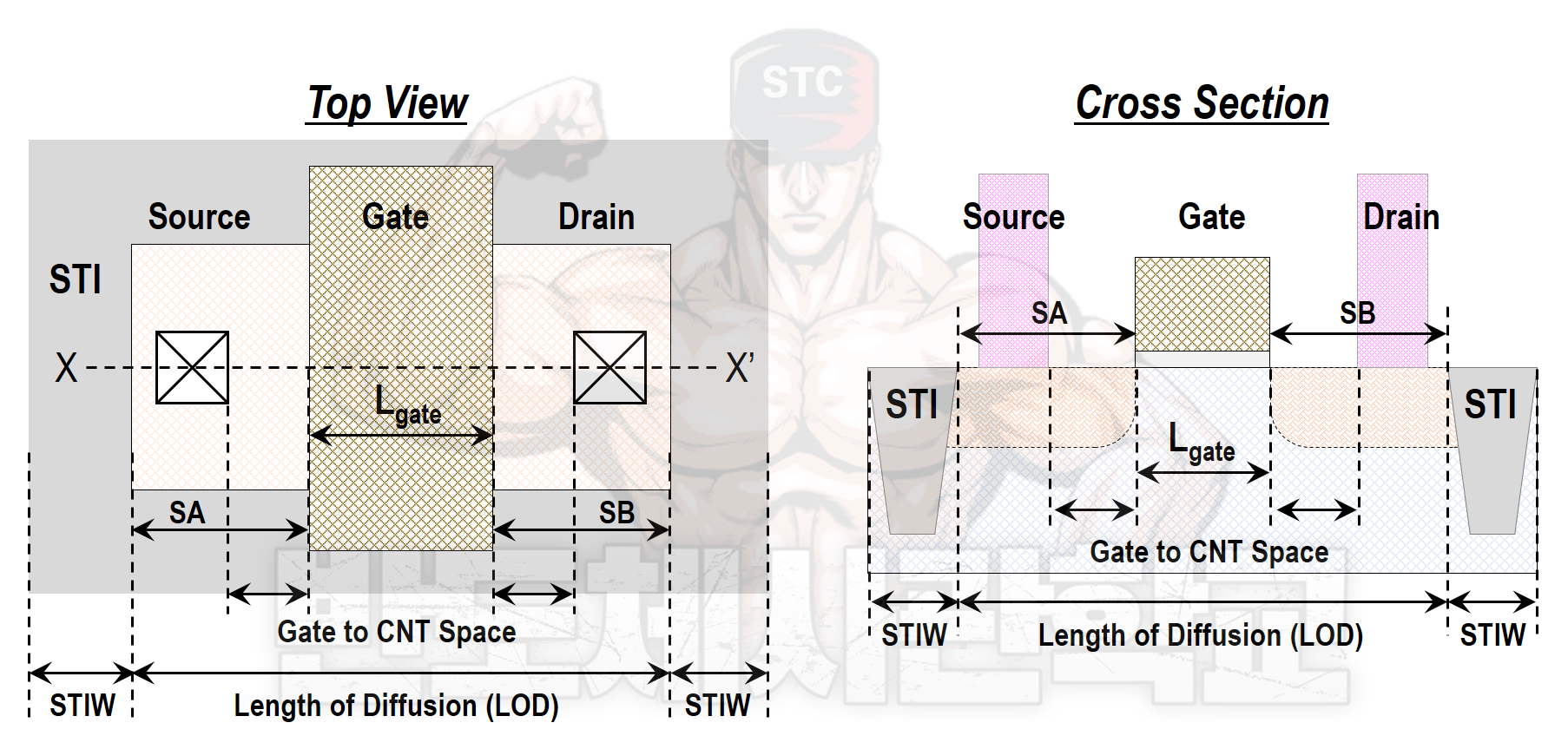

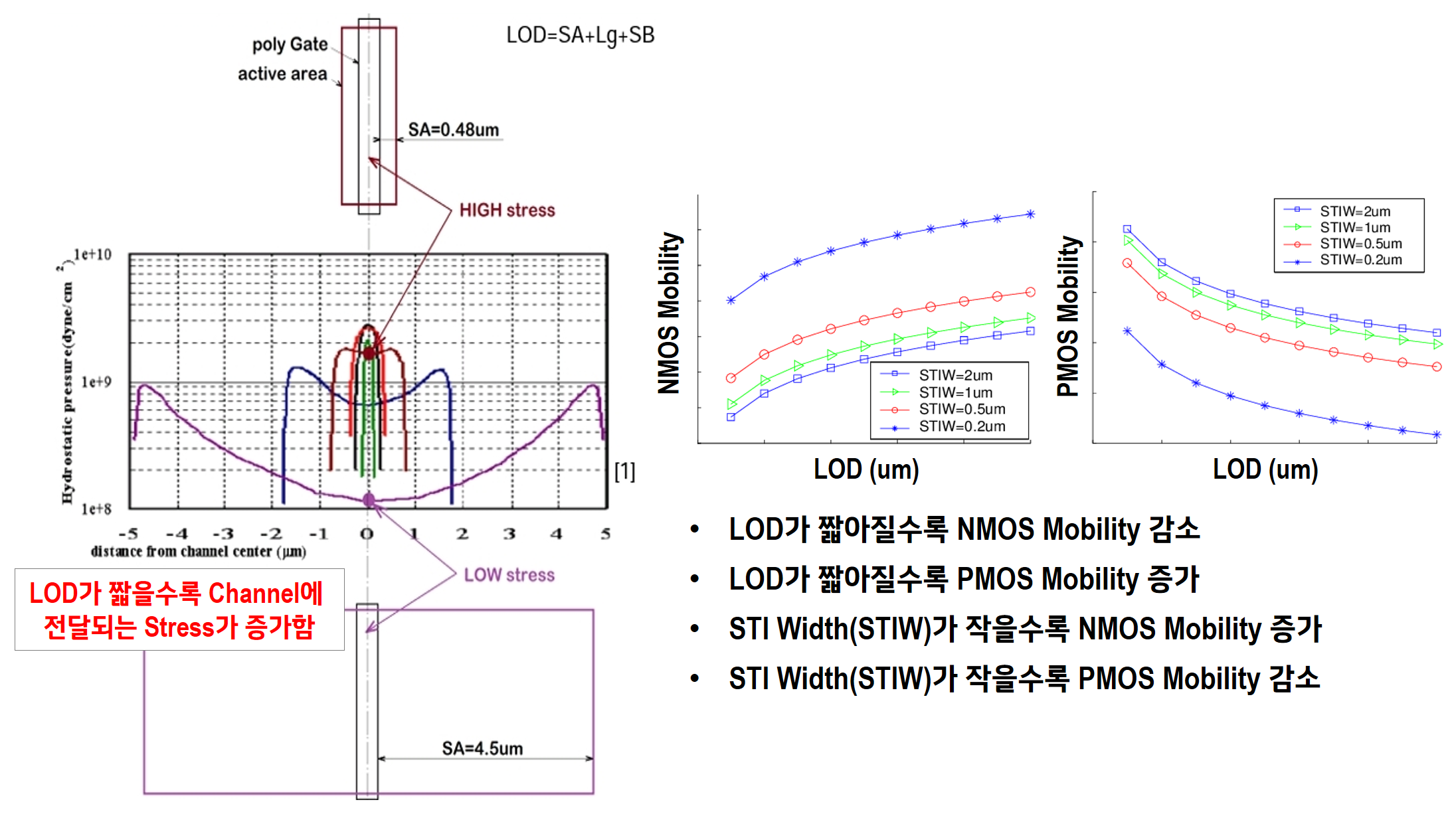

STI Stress Effect의 경우, Length of Diffusion (LOD)와 Gate to CNT Space 같은 Layout에 따라 Stress에 변화가 발생하여 Tr. 특성의 Variation이 증가되는 현상입니다. LOD는 Gate Length + S/D Diffusion를 합한 Size입니다. LOD에 길이에 따라 STI에 의한 Stress가 다르며, 그로 인해 Tr.의 Vth Variation이 심화됩니다. 또한, Gate to CNT Space은 Locally Strain을 완화시키기에, Gate to CNT Space가 가까워질수록 Current Variation이 심화됩니다.

- LOD에 따른 Stress 기인성 Vth Variation은 ~50mV, Gate to CNT Space에 따른 Stress 기인 Vth Variation은 ~10mV 수준입니다.

꼬리 3.1. STI Stress가 Device에 어떤 영향을 미치는지 메커니즘을 설명해주실 수 있나요.

Stress를 이용하여 소자 Performance를 향상시키는 기술이 바로 Strained MOSFET 기술입니다. 간략히 설명드리면, CESL(Contact Etch Stop Layer) 역할의 Nitride Layer를 이용하여, NMOS Channel에 Tensile Stress를 인가하여 Mobility를 향상시킬 수 있습니다. PMOS의 경우, SiGe Epi. S/D 형성하여 Channel에 Compressive Stress를 인가하여 Performance를 향상시킬 수있죠.

STI Stress 또한 동일한 영향이 가해집니다. LOD가 짧아질수록 Channel에 가해지는 Stress가 증가하고, 그로 인해 NMOS의 Mobility는 감소, PMOS의 Mobility는 증가하게 됩니다. STI의 Width가 증가할수록 Channel에 가해지는 Stress는 더 커지며, 마찬가지로 STI Depth가 증가할수록, Si Channel에 가해지는 기계적 Stress 또한 증가하여, Stress에 기인한 소자 특성의 Variation은 심화됩니다. 그로 인해, node Scaling donw 시 Device 간 Isolation을 위한 STI의 Depth가 점점 더 짧아져야 하는 이유 중 하나가 바로 Stress 기인 Variation이 되겠습니다.

- Length of Diffusion (LOD), STI Width, STI Depth에 따른 STI Stress는 Device의 Mobility Variation을 유발하며 이는 Logic Tr. 성능의 Variation을 초래합니다.

꼬리 3.2. STI Stress Effect을 개선할 수 있는 방법이 있나요.

STI Stress 기인 Variation을 개선할 수 있는 방법은 공정 Set-up 초기부터 STI Depth, Width, LOD Design을 조건별로 Split 하여 평가를 진행하여 Stress Effect이 최소화 되는 공정 조건을 잡는 수밖에 없습니다. 앞서 설명드렸듯이, 미세공정에서는 STI의 Depth가 점점 더 얇아지고 있는데, 미세 패턴 구현이 가능하다는 점과 Stress Variation이 최소화된다는 장점을 가지고 있습니다. 하지만, STI는 Device와 Device를 물리적으로 Isolation하는 기능을 하기 때문에 Depth를 무작정 줄이다 보면 인접 Device 끼리 서로 영향을 줄 수 있기에 STI Depth를 Shrink 하기 위해서는 Well의 Junction을 통한 Electrical Isolation을 보강한다던지와 같은 공정 최적화가 수반되어야 합니다.

질문 4. Layout 관점에서 공정 정합성을 향상시키기 위한 방법에 대해서 알고 있을까요.

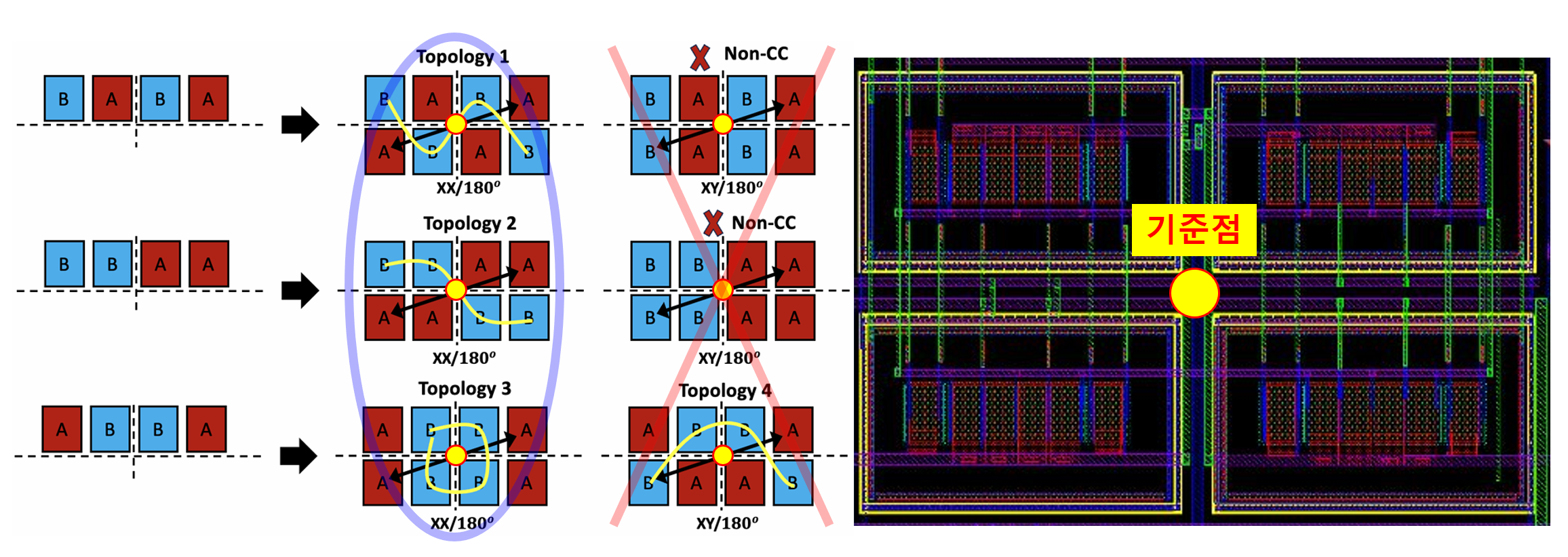

질문 주신 사항에 대해서 문득 3가지 방안이 떠올랐습니다. 첫 번째는 Common Centroid Layout (CCL) 기법입니다. CCL 기법은 공정 정합성을 향상시키기 위해 Physical Design 단에서 Layout 진행 시 특정 중심점을 기준으로 소자들을 대칭적으로 배치하여, 공정 Variation을 최소화 시키는 기법입니다. 공정 Variation이 Wafer 내에서 선형적으로 발생한다고 가정할 경우, 소자들을 대칭적으로 배치시킬 때 공정 Variation이 서로 상쇄시키면서 Matching 특성이 향상됩니다.

Common Centroid Layout 기법의 경우, Matching 특성이 특히 중요한 Differential Circuit, Current Mirror와 같은 Analog 회로에서 주로 적용됩니다.

꼬리 4.2. 3가지라고 하셨으니 계속 이야기해주세요.

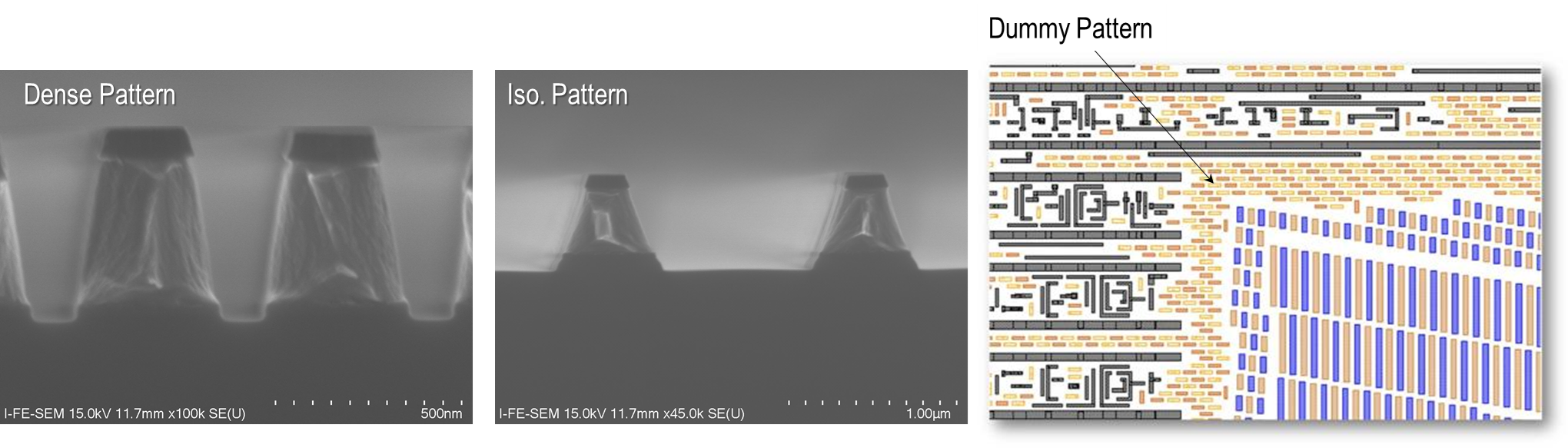

네. 다음 방법은 Dummy Pattern을 활용하는 방법입니다. 정합성을 해치는 요인 중 공정 Variation의 영향이 정말 크다고 생각합니다. 수많은 공정 Step 들이 존재하고 각각의 공정 Step에서 발생하는 Variation은 Mismatch를 심화시킵니다. 이러한 공정 Variation을 최소화 시키는 방법 중 하나는 바로 Pattern Density를 맞추어주는 것입니다. Etch 공정을 예로 들었을 때, 동일 공정 조건에서 동일한 CD Dimension을 Targeting 한다고 했을 때, Dense Pattern이냐 독립된 Iso. Pattern이냐에 따라서 Loading Effect가 발생하여 서로 다른 Etch Profile의 결과가 나타날 수 있습니다. 이를 개선하기 위해서, Dummy Pattern을 삽입함으로써 Pattern Density를 일치시키고 그로 인해 공정 Variation을 최소화하여 정합성을 향상시킬 수 있습니다.

- Desne Pattern과 Iso Pattern의 Etch Profile 차이

꼬리 4.3. 마지막 방법에 대해서 한 번 설명해주시죠.

이건 최근 본 논문에서 본 내용으로 인접 Tr. 간 상부 Metal Layer의 Coverage 비율에 따라 Tr. 성능의 Variation이 발생할 수 있다고 보았습니다. 메커니즘을 간략하게 설명드리면, Metal이 Tr. Active를 Coverage하는 비율이 클수록 Si/Sio2 Interface의 Dangling Bond를 Passivation하고 있던 Hydrogen의 Out Diffusion을 차단할 수 있다는 내용입니다. 따라서, 인접 Tr.간의 Mismatch를 개선시키기 위해서 Tr. 간 Metal Coverage 또한 동일하게 Drawing 해줌으로써 미비하지만 Device Matching성을 향상시킬 수 있다고 생각됩니다. (관련 논문은 Google 검색!)

공정 엔지니어라면 항상 공정 정합성에 민감해야 합니다.

공정 정합성을 저하시키는 여러 요인들과 그에 따른 Mechanism에 대해서 다루어 보았습니다.

우리 모두 성장하여 반도체 강국이라는 명성을 되찾아 옵시다!

오늘 하루도 고생하셨습니다.

반응형

그리드형(광고전용)

최근댓글