Wet etching 습식식각 방식은 세정이나 에싱 공정 분야로 발전했습니다. 반도체 회로 패턴을 구현하기 위해서 Plasma를 이용한 Dry etching 건식식각이 주류로 자리를 잡았습니다. 오늘은 패턴을 형성하기 위한 Dry etching에 대해서 설명해보겠습니다.

[질문 1]. Dry etching 건식식각에 대해서 설명해주세요.

포토공정에서 Photoresist 유기막은 하부막의 식각을 위한 마스크 layer로 활용됩니다. 반도체 적층구조에서 대부분의 박막들은 비정질이나 다결정 상태입니다. (대표적인 단결정은 Si wafer) 박막이 다결정이다 보니, Wet etching 시 등방성 etch profile 특성을 가지기 때문에 미세패턴 구현에 큰 제한이 있습니다. 그래서 Dry etching이 미세공정에서 중추 기술로 자리잡게 되었습니다. 대표적인 Dry etching은 ion bombardment 메커니즘을 활용한 ion milling 공정이 있으며, selectivity와 throughput이 낮다는 이슈를 개선하기 위해서 Plasma etching 기술이 채택되었습니다.

[꼬리 1-1]. Ion milling에 대해서 설명해주세요.

ion milling은 순수한 Ar+ 이온을 가속시켜 웨이퍼에 충돌시킴으로써 sputtering을 통해 에칭하는 공정입니다. Chamber 내부에 Ar gas와 같은 비활성 기체를 주입한 후 필라멘트를 가열해주면 hot electron이 튀어나와 가속됩니다. 고에너지를 가진 hot electron이 비활성 기체분자와 충돌하면서 Ar 원자를 이온화시킵니다. 이렇게 생성된 Ar+ 이온은 양극에 인가된 바이어스에 의해 가속되어 wafer를 때리게 됩니다. 이러한 과정을 ion bombardment라고 합니다. 순수하게 물리적으로 wafer 원자들을 떼어내면서 etching이 이어집니다. 이러한 ion milling은 dry etching 공정의 가장 기본이 되며, vertical profile 구현이 가능하지만 selectivity나 throughput이 낮다는 단점을 가지고 있습니다.

[질문 2]. Plasma etching 공정에 대해서 설명해주세요.

대표적인 Plasma etching은 Reactive Ion Etching, RIE 방식입니다. Plasma etching은 radical의 화학반응에 의한 등방성 etching과 이온 충돌에 의한 이방성 etching 모두 포함하고 있습니다. RIE 방식의 핵심은 직진성을 가지는 양이온이 식각 영역에 충돌함으로써 target 박막의 분자간 결합을 약화시킵니다. 분자간 결합이 약해진 부위에 반응성이 높은 radical이 흡착되고, 막을 구성하는 입자와 반응하여 휘발성 화합물이 생성되면서 gas로 배출됩니다. Plasma etching의 가장 큰 장점은 ion milling과 같이 양이온만으로 식각하는 것과 혹은 radical 식각을 각각 별도의 공정을 진행할 때보다, 양이온의 물리적 작용과 Radical의 화학적 반응을 병합해 동시에 물리화학적 방식으로 etching할 경우, Etch rate이 10배 가까이 높아집니다. 이는 양이온의 물리적 반응에 의한 이방성 식각과 화학적 반응에 의한 우수한 selectivity와 높은 throughput을 가지는 특징을 가지기 때문에 선단공정에서 채택된 에칭기술 할 수 있습니다.

[꼬리 2.1]. Radical이 등방성 식각이면 wet etching 같은 이슈가 발생하는거 아닌가요.

물론 그럴 수 있습니다. Radical은 target 박막과 화학반응을 통해 등방성 에칭이 됩니다. Radical이 등방성 etch profile을 가지지만 양이온의 충돌에 의해 분자간 결합이 약해진 부분이 Radical에 더 쉽게 포획되어 반응이 쉽게 일어납니다. 이러한 이유로 Vertical profile 구현이 가능한 것입니다. 포획된 입자들은 radical과 함께 휘발성 화합물이 돼서 gas 형태로 표면으로부터 탈착되어 진공의 힘에 의해 배출됩니다.

[꼬리 2.2]. Etch rate과 핵심 성능지수에 대해서 설명해보세요.

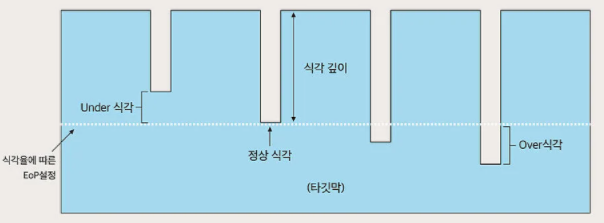

Etching 공정에서 가장 중요한 것은 바로 Uniformity입니다. etch uniformity는 수율과 바로 직결되기 때문입니다. 하지만 etching 공정을 진행하면서 wafer 상의 etching 깊이가 다를 수 있습니다. 따라서 평균 etch rate과 depth를 고려하여 etching이 종료되는 End of Point, EOP를 설정하는 것이 매우 중요합니다. EOP를 설정했다 하더라도, 특정 단차를 가지는 profile이나, 패턴 밀도에 따라 Over etch나 under etch가 될 수 있습니다. 그리고 식각의 핵심 성능지수로는 selectivity가 있습니다. mask 역할을 하는 PR유기막, 산화막, 질화막 등의 식각률 대비 target 막의 식각률로 선택비가 높을수록 target 박막의 식각이 빠르게 진행될 수 있습니다. 미세화가 될수록 더 높은 selectivity가 요구되고 있으며, Plasma etching의 경우, 양이온의 충돌로 인해 selectivity가 떨어지지만 Radical에 의한 etching의 selectivity가 높으므로 Plasma etching이 핵심공정인 이유입니다.

"Over etch가 under etch보다 유리할 수 있습니다. 그 이유는 식각이 덜 된 under etch는 다음 후속공정인 ion implant 공정에 큰 영향을 미치기 때문입니다."

그리고 식각의 미세패턴의 밀도가 낮은 영역일수록 식각이 원활합니다. 이는 "Loading effect"로 설명할 수 있는데, 여기서는 간단하게 설명드리고 다음 포스팅에서 자세히 설명드리도록 하겠습니다. plasma 내의 양이온과 radical의 밀도는 균일하고 한정 돼있습니다. 하지만 위와 같은 depth profile의 밀도가 높을수록 etching 공정에 참여하는 source들이 부족해 충분한 깊이로 파내지 못하기 때문에 under etch 현상이 심해집니다. 이는 후속공정인 이온주입 공정에 부정적인 영향을 미칩니다. 따라서 한 웨이퍼 내 에서 웨이퍼와 웨이퍼 간의 etch rate의 uniformity가 매우 중요한 이유입니다. 공정엔지니어로서 이러한 공정조건들을 고려하여 etch rate의 uniformity를 최대한 높이는데 주력해야 합니다.

[질문 3]. Plasma etch process에 대해서 간략하게 설명해주세요.

① 웨이퍼를 800~1,000℃ 온도의 산화공정을 통해 웨이퍼 표면 상에 높은 절연 특성을 가지는 SiO2 막을 Dry oxidation으로 형성합니다.

② 증착공정을 통해 산화막 위로 poly-Si 혹은 전도성을 가지는 박막을 CVD or PVD 공정으로 증착합니다. Poly-Si의 경우 불순물 doping을 통해 전도성을 향상시켜줍니다.

③ Photo lithography 공정을 통해 PR 유기막을 코팅하고 노광공정을 통해 PR유기막에 회로패턴을 전사합니다. PR 유기막에는 마스크의 회로패턴이 전사된 상태입니다.

④ 포토공정을 마친 웨이퍼를 Dry etching 합니다. 보통 Reactive Ion Etch, RIE 방식으로 진행하며, 박막별로 etchant gas를 달리하여 반복 진행합니다.

-DRAM의 Capacitor를 형성할 때는 ALD 공정의 Step coverage를 높이기 위해 여러 번의 증착과 여러 번의 etching 공정을 진행하는 것처럼, 반대로 식각의 aspect ratio를 높이기 위해 건식식각과 습식식각을 여러번 반복 진행합니다.

⑤ Trench 내부에 존재하는 polymer를 제거하기 위해 중간중간에 cleaning 공정을 진행해줍니다.

-세정용액이나 Plasma source들이 trench 밑바닥까지 내려갈 수 있도록, 재질, 소스, 시간, 형태, 순서 등 모든 공정변수를 고려하여 유기적으로 최적화시켜야 합니다. 이 중 변수가 하나라도 이상이 생기면 그에 따른 변수들도 다시 제어해야 하기 때문에 step 별로 요구조건을 충족시키도록 반복수행합니다.

"최근 ALD 공정 도입으로 박막 두께의 정밀 제어가 가능해지면서 점점 박막 두께가 얇아지고 있습니다. 뿐만 아니라 새로운 소재들이 도입되면서 재질은 강해지고 있습니다. 향후 Etching 공정은 낮은 온도와 낮은 압력을 이용한 기술로 발전하고 있습니다. FinFET, 2D-Xnm, 3D-Stacking 등 제품별로 공정 환경이 다채로워지며, 새로운 소스 개발 및 고선택비의 맞춤형 식각이 활발히 진행되고 있습니다. 식각의 목적은 미세한 패턴을 새기는 것으로 Critical Dimension, CD 제어와 Etching 공정 이후에 다음 공정을 진행하는 데 있어 under etch와 같은 문제가 없어야 합니다."

[질문 4]. 더 높은 수준의 etching 기술이 요구되는 이유에 대해서 설명해주세요.

Aspect ratio를 통해서 말씀드리겠습니다. 우선 Aspect ratio는 종축 대비 횡축의 길이 (높이/밑변의 길이)의 비율을 의미합니다. 회로 선폭이 점점 작아지면서 Aspect ratio가 큰 좁고 깊은 구조가 요구되고 있습니다. 따라서 초미세화 혹은 고밀도가 요구되는 차세대 제품의 경우, 식각 과정에서 하부막을 양이온이 파고들어 갈 수 있을 정도로 매우 높은 종횡비를 구현해야 합니다. 회로 선폭 10nm 미만의 초미세 tech node를 구현하기 위해서는 DRAM의 Capacitor의 종횡비는 100이상을 유지해야 합니다. 낸드플래시의 경우 3D 역시 셀의 256단 적층 이상을 구현하기 위해서는 높은 Aspect ratio가 요구됩니다. 소자나 제품기술 혹은 다른 공정기술에서 요구 수준을 달성했다 하더라도, 식각공정에서 요구사항을 충족시키지 못하면 제품을 생산할 수 없습니다. 그래서 선단공정에서 식각공정의 하이테크가 요구되는 이유입니다.

'반도체사관학교 훈련과정 > 반도체 전공정' 카테고리의 다른 글

| [식각공정] 훈련 5 : Conductor & Dielectric Etch 방법 + ICP vs. CCP Type Plasma (28) | 2022.04.11 |

|---|---|

| [식각공정] 훈련 4 : "Reactive Ion Etching, RIE 공정에 대해서 설명하세요" (16) | 2022.04.11 |

| [Yield] : PCM, SPICE Modeling, Corner Margin 평가 (0) | 2022.04.01 |

| What Are The Process Corners in VLSI Design (2) | 2022.03.28 |

| [포토 공정] Photo Lithography 공정, 불량 사례 (0) | 2022.03.28 |

최근댓글