현재 반도체 파운드리 업계 점유율의 50% 이상은 TSMC가 점유하고 있죠. 그리고 이를 맹추격하는 삼성과 새롭게 시장을 뛰어들어 기회를 엿보는 인텔의 공격적인 투자로 파운드리 시장은 말 그대로 치열한 경쟁구도에 있습니다.

그렇다면 현재 파운드리 시장의 막강한 점유율을 가지고 있는 TSMC는 어떻게 준비하고 있을 지에 대해서 다루어보도록 하겠습니다.

TSMC가 공개한 다양한 자료와 수치적 Data로 미루어 보았을 떄, 2nm 공정의 수율은 60% 이상 달성했다고 하는데, 어떤 기술적 Issue가 있었고, TSMC가 이를 어떻게 Challenge 했는지 다루어 보도록 하겠습니다.

최근 TSMC는 미국에서 열렸던 'IEDM 2024'에서 하나의 논문을 발표합니다. (이는 구글링을 통해 쉽게 찾아볼 수 있습니다). 이 논문의 핵심 Keyword는 우리 딴사관에서 항상 중요하게 다루었던 공정 경쟁력인 Power (전력), Performance (속도), Area (집적도)인 PPA 관점에서 이야기 해보고자 합니다.

여러분들처럼 반도체 엔지니어의 커리어를 꿈꾸는 분들이라면 'Trade-off'라는 용어가 익숙하실 것입니다. Performance를 높이기 위해서는 Logic Tr.의 보다 높은 구동 전류가 필요하고, 향상된 속도만큼 전력소모도 증가하기 마련이죠. Area를 Shrink 하여, 보다 많은 Net-die를 확보하고 Cost를 인하하여 제품 경쟁력을 확보하는 것이 중요하지만, 역시 작아진 Size만큼 Subthreshold Leak. Junction Leak.의 증가로 인해 Power 경쟁력은 저하되기 마련입니다.

그런데, TSMC가 발표한 논문은 상당히 흥미롭습니다. 결론은 TSMC의 2nm node인 N2 공정에서 '2nm node에서 더 작은 반도체를 만들기 때문에 Power와 Performance 모두 경쟁력을 강화할 수 있었다'라고 말하죠. 우리가 요즘 Short Channel Effect을 질리도록 접하다 보니, 'PPA 경쟁력이 모두 향상됐다고?' 의아해 하실 수 있을텐데요. 그 이유는 한 번 게시글을 통해 다루었던 것 같습니다.

Tip) Short Channel Effect가 발생하지 않으려면..?

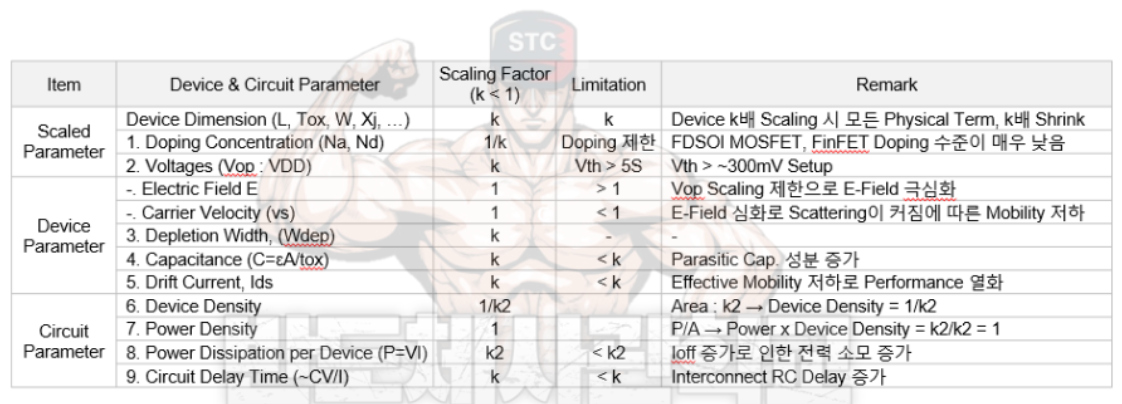

우리가 기존 소자보다 더 소자 Size를 Shrink 했을 때, Shrink 하기 전 소자와 동일한 Power, 동일한 Performance를 가지기 위해서는 소자 내부의 Electrical Field가 변하지 않으면 된다고 말씀드렸습니다. 눈부신 공정기술 설비의 혁신으로 Physical Dimension을 더 작게, 아주 미세하게 구현이 가능하게 되었죠. 하지만, Physcial Deimension이 Shrink 되면서 그에 따른 E-field는 점점 더 커지게 됩니다. 그래서 아래와 같은 여러 Parameter에 대해서 Shrink를 위한 Scale Factor가 적용되어야만 하죠. 하지만 문제가 발생하게 됩니다.

① Size가 작아지니 Doping이 잘 이루어지지 않습니다. 우리가 알고 있는 Doping 행위의 Mechanism은 '치환형'입니다. 주입된 Dopant 원자가 결정격자를 이루고 있는 Si의 결합을 치고 들어가야 과잉의 전자 혹은 정공을 만들어내는 것이죠. 하지만 Size가 점점 더 작아지니 Dopant 이온이 Si 결정원자와 치환될 확률 자체가 줄어들게 되죠.

② Vop 를 쉽게 줄일 수가 없습니다. 집적도가 높아지면서 점점 더 Multi-function 구현에 대한 요구사항이 늘어나고 있습니다. 뿐만 아니라 높은 Clock Freq.가 요구되면서 전력소모는 점점 더 증가하고 있죠. Low Power를 달성하기 위해서는 Vop를 낮추거나, 의도치 않은 Leakage 성분을 Control해야 합니다. 여기서 한 가지 중요한 문제는 우리가 쉽게 Vop를 낮출 수 없다는 점입니다. 그 이유는 바로 node shrink를 한다고 하더라도 Threshold Voltage를 낮출 수 없기 때문입니다.

Logic 연산이 가능하기 위해서는 Ioff 대비 Ion은 10E+05 이상이 되어야만 합니다. Ioff일 때의 Vgs=0V, Ion일 때는 Vgs=Vth의 전압이 인가되겠죠. Ion ≥ Ioff * 10e+05 의 조건을 만족시킨다는 것은 Vth ≥ 5S를 만족해야 한다는 말과 동일합니다. 여기서 S는 여러분들이 흔히 알고 있는 Subthreshold Swing(S)의 값이죠. (Drain Current를 10배 증가시키기 위한 최소 Gate Voltage). 하지만 우리는 Field Effect의 Mechanism으로 동작하는 FET 소자(Planar, FinFET, GAA 등)는 S≥60mV/dec의 한계를 가진다는 것을 배우셨을 것입니다.

따라서, 아무리 Ideal한 소자를 만든다고 해도, Vth ≥ 5S = 5*(60mV) = 300mV의 값을 가진다는 다는 것을 의미하죠. 무턱대고 우리가 소자 내부의 E-field를 낮추기 위해서 Vop를 낮추게 된다면 소자 내 구동 전류를 충분히 흐르게 할 수 없어 Performance 경쟁력이 열화될 수 있습니다.

그렇다면 TSMC는 어떤 방식으로 2nm node에서 PPA 경쟁력을 모두 거머 쥘 수 있었을까요.

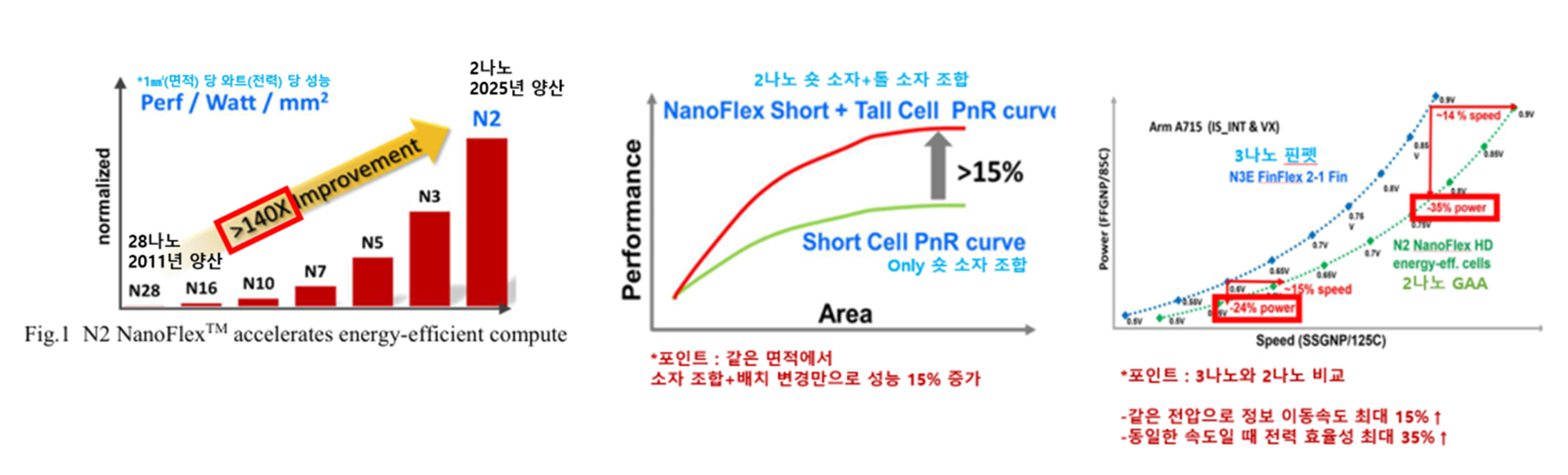

먼저, TSMC에서 발표한 수치적 Data를 기반으로 설명드리겠습니다. TSMC의 2nm 공정(N2)을 적용했을 때 동일 면적(mm2), 동일전력(W) 조건에서, Performance가 28nm 공정 대비 140배 개선되었습니다. 동일 면적에서 소자의 조합과 배치 변경만으로도 성능을 15% 증가시킨 결과가 있었으며, node인 3nm에서 동일 전력 조건에서 Speed는 최대 15%, 동일 Performance에서 전력 효율성은 최대 35% 향상된 결과를 얻었습니다.

위에서 언급했던 'Short Channel Effect가 발생하지 않으려면...?'의 돌파구는 무엇일까요. 여러분들도 아시다시피, TSMC, 삼성, 인텔 등 파운드리 업계에서 채택한 방법이 바로 Device Structure의 혁신이죠. 그 중 TSMC, 삼성, Intel 만이 Gate-All-Around (GAA)라는 기술적 Edge Leading을 주도하고 있습니다. GAA는 삼성전자가 Multi-Bridge Channel FET (MBCFET)으로 22년도 처음 적용한 소자 구조입니다. GAA 구조는 Gate가 Channel 전면을 감싸고 있기 때문에 (Cox=A(↑)/tox), Gate가 Channel에 행사하는 영향력이 증가하기에, 효과적으로 Subthreshold Leakage Current를 억제할 수 있죠. Planar/FinFET 대비 GAA는 Oxide Capacitance가 구조상 더 크기 때문에 Field Effect 특성이 향상되고 Circuit을 Shrink 한다 하더라도 기존 소자 대비 SCE에 대한 Immunity가 높을 수밖에 없죠.

TSMC는 이러한 GAA 소자 장점 외에 고객사의 유연한 공정 사용을 위해 다양한 Option 소자들을 개발하였습니다. 바로 'Tall Cell'과 'Short Cell'의 소자를 각각 Option 소자로 두어, 높은 구동전류의 Tall Cell 소자는 HPC 분야에, 비교적 적은 구동전류량을 가지는 Short Cell 소자는 Low Power 분야에 사용될 수 있도록 설계하여 다양한 Application의 범위의 고객사를 확보하기 위한 노력도 보였습니다. 뿐만 아니라 동일 IC 내에 Short/Tall Cell 소자를 적절히 PnR 하여 VCO 영역과 같이 High Freq.가 요구되는 Block에는 Tall Cell 소자, 그렇지 않은 영역은 Short Cell로 배치시킴으로써 고객사 IC 경쟁력도 확보할 수 있는 전략을 내세웠습니다. (Short+Tall 소자 조합으로 설계했을 때, Only Short 소자 조합으로 설계 대비 Performance가 15% 개선되었음 보여줌)

2nm N2 Device Key Feature

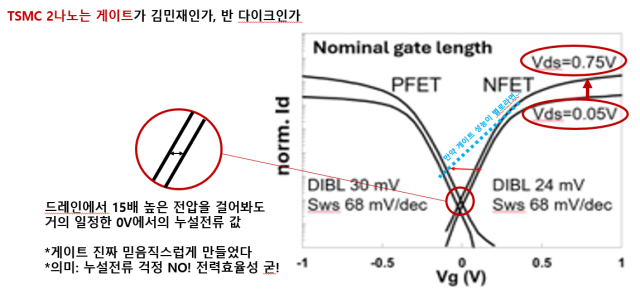

Short Channel Effect의 정도를 검토하기 위한 Item으로 DIBL과 Subthreshold Swing, Gds, Delay 등 여러 Item들로 평가할 수 있습니다. 그중 DIBL 특성을 보시면, NFET의 경우 DIBL 24mV/V, PFET은 30mV/V 값을 가지는 것을 확인할 수 있습니다. 이 값을 풀이해보면 Drain Voltage를 1V 증가시킬 때, NFET의 경우 24mV 감소 PFET은 30mV 감소함을 의미합니다.

즉, Linear 상태일 때와 Satruation 상태일 때의 Threshold Voltage 차이가 거의 없음을 나타냅니다.

제가 여러분들에게 항상 Short Channel Effect는 Gate와 Drain이 만들어 내는 E-field 간의 싸움이라고 이야기를 했습니다. Vth roll-off, Subthreshold Leak., Hot Carrier 등 대표적인 Short Channel Effect는 Drain에 의한 영향력이 Gate보다 우세해지면서 발생하는 현상들이라고 해도 과언이 아닙니다. 그런데, DIBL이 20~30mV로 작다는 것은 Gate의 영향력이 Drain 대비 압도적으로 크다는 것을 의미하고, 이는 역시 Gate가 Channel 전면을 감싸는 Gate-All-Around 구조를 아주 잘! 만들었기 때문이라고 나오는 특성이라고 생각됩니다.

여러분들이 공정엔지니어가 돼서 공정을 Set-up하고 검토하는 기회가 온다면 DIBL 20~30mV 값은 엄청 작은 값이라는 것이라는 것을 알게 될 것입니다.

Subthreshold Swing 특성은 N/PFET 모두 68mV/dec. 특성으로 발표했습니다. SS는 해당 공정의 소자가 얼마나 Ideal한 소자에 근접한 특성을 냈는지 평가할 때 주로 사용됩니다. Ideal한 FET 소자는 60mV/dec의 한계를 가진다고 말씀을 드렸는데요. 68mV/dec 수준이면 어느 정도 Ideal 소자 특성에 범접했다라고 생각됩니다. SS 값이 ~60mV/dec.에 가까워지기 위해서는 여러분들도 아시다시피 Subthreshold Leak. Current를 엄청나게 낮춰야겠죠.

또 다른 표현을 빌리자면, Drain Current를 10배 향상시키기 위한 최소 Gate 전압이 작아진다는 말이기 때문에, 더 작은 전압으로도 원하는 Performance를 달성할 수 있죠. 따라서, 더 작은 전압으로 Target Performance도 달성함과 동시에 Low Power를 달성할 수 있는 것입니다.

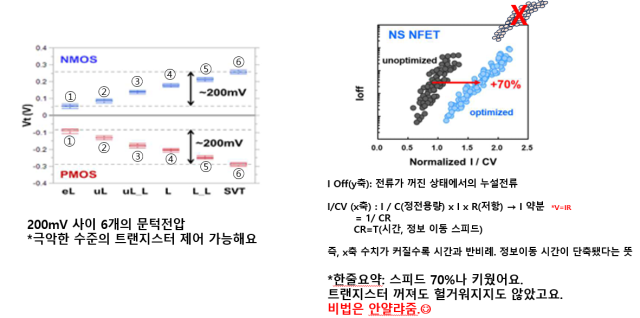

일반적으로 공정을 Set-up할 때는 다양한 Vth Option의 소자들을 제공합니다. High Vth (HVT), Regular Vth (RVT), Low Vth (LVT), Ultra Low Vth (ULVT), Super Low Vth (SVT) 등과 같이 다양한 Vth의 Option 소자를 제공함으로써 파운드리를 이용하는 고객들 자사 IC에 맞는 소자들을 선택하고 설계함으로써 제품 경쟁력을 확보할 수 있도록 여러 소자들을 제공합니다. (Fab마다 Device Option에 대한 고유 표기 방법이 다를 수 있습니다.)

TSMC는 N/PFET에 대해서 200mV 전압 Range 내에 6개의 Vth Option을 제공합니다. 200mV 범위 내에 6개의 Vth Option이면 각 Option 소자 별로 최소 30mV 수준으로 구분되고, Vth의 Tolerance가 상당히 Tight하게 관리되고 있다는 것을 나타냅니다. 일반적으로, Vth Option 소자 간 Vth offset은 50~70mV 수준입니다. 위 Data만 보아도 TSMC가 얼마나 정확하게 Vth를 Targeting 할 수 있고 산포 관리를 할 수 있는지 TSMC만의 우수한 공정능력을 낱낱이 보여준다고 해도 무방합니다.

공정 평가 시 전력 당 성능(Performance/Watt) 개선을 나타내는 전성비 결과 입니다. 3nm 대비 2nm GAA에서 Watt당 Performance 성능이 월등이 우수한 결과를 확인할 수 있습니다. 위에서 언급했던 것과 같이 동일 전력으로 더 우수한 Performance를 낼 수 있고, 달리 말해 더 적은 에너지로 동일 Performance를 낼 수 있음을 의미하죠.

지금까지 말한 내용 모두, 3nm 공정 대비 Low Power, High Performance, Area Scaling 즉 PPA 측면에서 공정 경쟁력이 모두 우세한 공정을 TSMC가 발표했다는 것입니다.

'반도체사관학교 훈련과정 > 반도체 전공정' 카테고리의 다른 글

| TSMC 2nm N2 공정, 그들만의 경쟁력은 무엇일까요?. 면접 전에 꼭 한 번 읽고 가야 할 내용 (0) | 2025.01.30 |

|---|---|

| [딴사관 정주행 프로젝트] CMP 공정 + 세정공정, C&C (0) | 2024.11.27 |

| [딴사관 정주행 프로젝트] 반도체 공정 -"에치공정, 기초+심화 편" (0) | 2024.11.26 |

| [반도체 공정] C&C (Cleaning & CMP) 공정의 모든 것, 한눈에 이해하는 CMP 공정 (1) | 2024.11.13 |

| [딴사관 정주행 프로젝트] 플라즈마 (Plasma) 기초부터 심화까지. (0) | 2024.11.10 |

최근댓글